PC-8001mk2用に素敵なデモプログラムが公開されました。mk2用といいながらNモードで動くとのことです。ただN-BASIC ROMの裏RAMを使用しているとのこと。これは仕様を合わせたメモリーボードを作ればわたしの愛機PC-8001無印でも動くのでは?!

きらびぃさんのアルファデモ

きらびぃさんが、PC-8001mk2用として作られたアルファデモが公開されております。もともとはPC-8801mk2SR用ゲームのデモをPC-8001mk2のNモードで実現したというものであります。

グラフィックはPC-8001無印と同じセミグラフィック。音楽はPCGの3声をお使いの模様。これは、ぜひわたしの愛機PC-8001無印でも動かしてみたい!

ちなみにプログラム類は以下で公開されております。wavデータもあるのでPC-8001でもCMT経由でロードできるはず。

きらびぃさんデモの動作要件

きらびぃさんのデモですが、PC8001mk2用のものは0000h番地~7FFFh番地のN-BASIC ROMの裏側にあるRAMを使う仕様となってまして、64kBフルにメモリーが装備されていることが前提となっています。ROM/RAM切り替えはPC-8001mk2の仕様に準拠しておりまして、以下のようにI/Oアドレス0E2h番地へデータを出力することで制御します。

| 0E2番地への出力データ | 裏RAMの読み書き |

| 00h | 読み書きとも禁止(読み出しはROM) |

| 01h | 読み出しのみ許可 |

| 10h | 書き込みのみ許可(読み出しはROM) |

| 11h | 読み書きとも許可 |

実は上記の仕様は、PC-8001の拡張ボックス PC-8012のメモリー制御に準拠しておりまして、わたしが数十年前から持っている以下の書籍にも記載がありました。ずっと何が書いてあるのかよく分かってなかったのですが、裏RAM(0000h番地~7FFFFh番地)の制御のためだったんですな。

数十年ぶりにスッキリしました。(以下の書籍には”PC8012のバンク切り替え方法”と出てました。)

PC-8001(無印)用 128kBメモリーボード

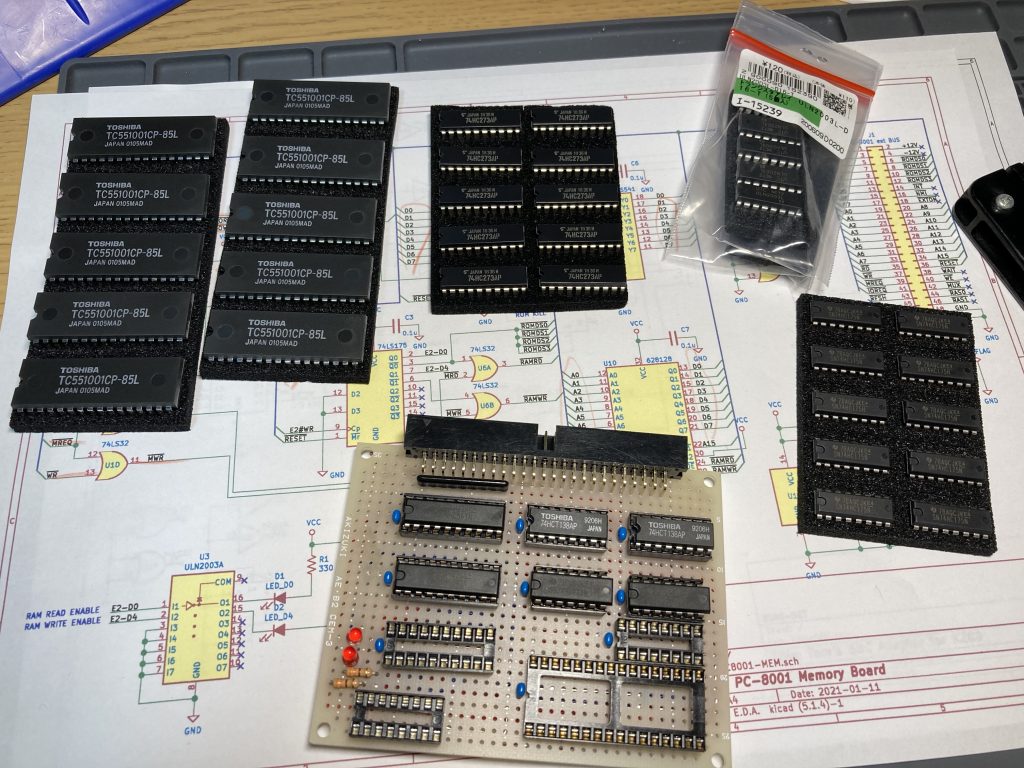

愛機PC-8001(無印)の拡張CPUバスにつながるメモリーボードを考えてみます。せっかくなので、32kB x4バンク分のメモリーボードにしてみたいと思います。KZ80-1MSRAMボードでも使用した1Mbit SRAMをつかうと4バンクとれそうです。しかも、なんと秋月電子で1Mbit SRAMが破格の値段で出ています。(2021年1月現在)

また、若松通商やオレンジピコショップでも1Mbit SRAMは入手可能であります。あとおすすめしませんが、根性のある方は秋月電子で売ってるSOPパッケージの1Mbit SRAMをDIP変換基板にはんだ付けするという手もあります。幅が合わなかったりで苦労しますけど…

バンク切り替えの方法

バンク切り替えの方法ですが、PC-8801のメモリーボードの仕様に合わせておこうと思います。I/Oアドレス0E3hにバンク番号を出力するというのが仕様らしいです。以下のページにPC-8801用128kBメモリーボードを自作された方がいらっしゃいまして、参考にさせていただきました。

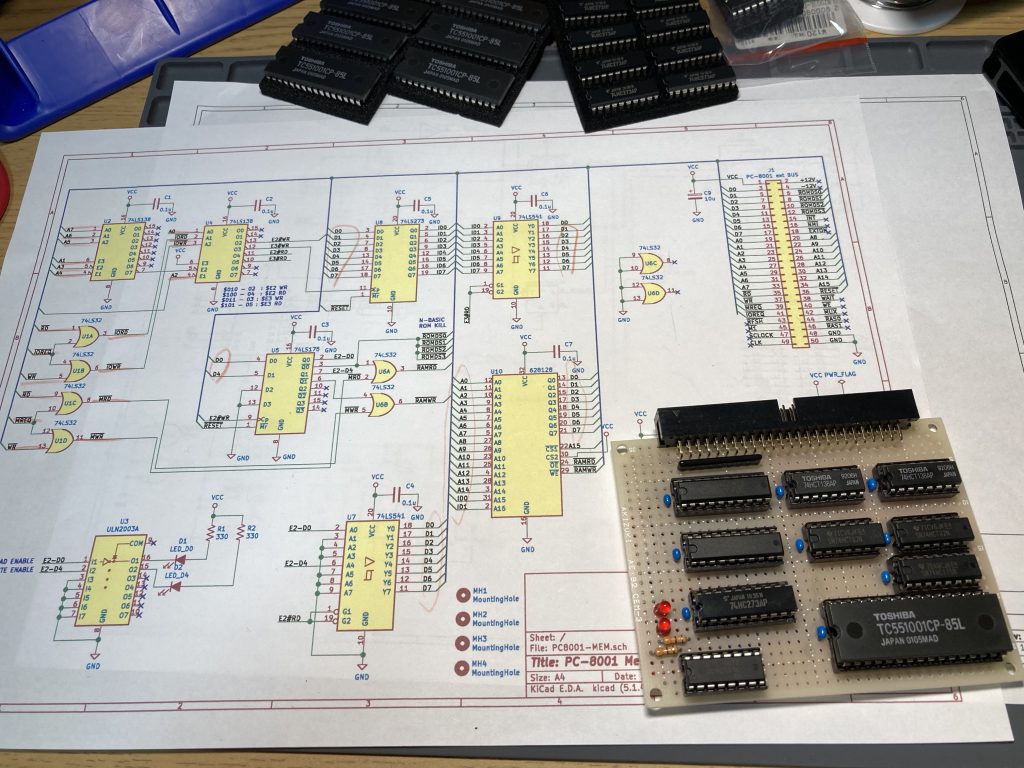

メモリーボードの回路について

PC-8001用メモリーボードですが、以下のような回路を考えました。

- アドレスデコーダーは、74LS138(74HCT138)の2段構成となってまして、I/O入出力に関係するアドレスバス信号(A0~A7)とIORD(I/O読み取り)、IOWR(I/O書き込み)信号で、0E2hや0E3hへの読み書き信号を作り出しています。

- IORD(I/O読み取り)、IOWR(I/O書き込み)信号はいつもの74LS32 ORゲートでZ80信号線(IOREQ、RD、WR)から作り出します。

- 0E2hへのI/O書き込み(N-BASICだとOUT命令)の際は、データバスD0、D4の信号を74LS175 で保持します。これが拡張RAMの読み、書きのための設定となります。

- 0E3hへのI/O書き込み(N-BASICだとOUT命令)の際は、データバスのD0~D7の信号を74LS273で保持します。これがバンク番号を保持するバンクレジスタとなります。今回のボードでは4バンクしかありませんのでD0、D1の信号だけが有効です。

- 0E2h、0E3hへのI/O読み取り要求(N-BASICだとINP関数)が来た場合、保持している情報をデータバスへのせるため、それぞれ74LS541(3ステートバッファ)をつないでいます。74LS541(3ステートバッファ)はI/Oアドレス0E2hや0E3hへのI/O読み取り要求が来た時だけActiveになるようにしています。

- 1Mbit SRAMはアドレスバス(A0~A14)、データバス(D0~D7)と直結しています。メモリーのA15、A16端子はバンクレジスタとなっている74LS273で制御します。リセット時はバンクレジスタはゼロクリアされているので、バンク0(A15=0、A16=0)が選択されています。

- SRAMメモリーは0000h~7FFFhまでのアドレスで動きますので、チップイネーブル端子(CS1)へアドレスバスのA15信号線を直結します。読み取り、書き込み信号はいつもの74LS32 ORゲートでZ80信号線(MREQ、RD、WR)から作り出した信号と、74LS175 で保持したRAMの読み、書きのための設定信号とのORをとって制御しています。

- 74LS175 で保持したRAMの読み、書きのための設定信号で、「RAM読み出し可能」の場合はPC-8001内のROMをディセーブルにする必要がありますので、PC-8001拡張CPUバスのROMDS0、ROMDS1、ROMDS2、ROMDS3信号線をLに落とします。

- ULN2003AはトランジスタアレイのICで、RAM読み出し、書き出しの状況を目で見てわかるようにLEDを点灯させてみました。

本回路図や、後述するN-BASIC COPYテストプログラムなどはいつもようにgithubで公開しています。ご覧ください。

バンクレジスタやRAM制御レジスタ

バンクレジスタやRAM制御レジスタには74LS273や74LS175を使用しています。データを保持するタイミングとなるCp端子のデータシートを見るとLからHへの立ち上がりがトリガーとなっています。

ただ、回路図を見てわかる通り、今回は74LS138でアドレスバスとI/O読み・書き信号を合わせてデコードされた信号線を入れてまして、デコードされた時にはLレベルへ落ちるはず。はて?これでうまく動くんだっけ?というところをZ80のデータシートを見てますと…

Z80データシート

Z80の信号線は上記のような動きとなってまして、アドレスデコーダ74LS138の出力はT2サイクルの途中でHレベルからLレベルに落ちて、T3サイクルでLレベルからHレベルに上がると想定されます。

T3サイクルの時点ではデータバスはまだ確定したままですので、バンクレジスタやRAM制御レジスタにした74LS273や74LS175に正しいデータが保持されるはず。

…..というわけでデコーダの74LS138の出力にNOTゲートをつけなくても良いということがわかりました。

ユニバーサル基板で作ってみた

回路図を引いてみたものの、いつもどおり作ってみないことには動くかどうかわからないわけで、秋月電子通販で購入したBタイプ片面ユニバーサル基板で試作してみたであります。

ちなみに手持ちに74LSタイプのロジックICがなくて、74HCTタイプ、74HCタイプで組んでいます。データバスをボックスヘッダのところでプルアップしておいたので、いけるかなと….

上記の機械語モニターが表示された画面は以下のようなN-BASICのROM領域を裏RAMへCOPYするプログラムを手打ちして実行して、0番地とか6000h番地を書き換えてフルRAMになったか確認しているところです。

1/ 0 : ;

2/ 0 : ; N-BASIC COPY & RAM START

3/ 0 : ;

4/ 0 : ;

5/ 0 :

6/ 0 : CPU Z80

7/ 0 :

8/ 0 : ="Z80" TARGET: equ "Z80"

9/ 0 :

10/ 9000 : org 9000h

11/ 9000 :

12/ 9000 : START:

13/ 9000 : 3E 10 LD A,10h

14/ 9002 : D3 E2 OUT (0E2h),A

15/ 9004 : 21 00 00 LD HL,0000h

16/ 9007 : 11 00 00 LD DE,0000h

17/ 900A : 01 00 60 LD BC,6000h

18/ 900D : ED B0 LDIR

19/ 900F : 3E 11 LD A,11h

20/ 9011 : D3 E2 OUT (0E2h),A

21/ 9013 : C3 66 5C JP 5C66h

22/ 9016 : END通常はN-BASIC ROMがある0番地とか、空きROMエリアになってる6000h番地がRAMに変わったことで変更した値が反映されることが確認できました。

PC-8001同梱の機械語モニターは貧弱ですが、最低限RAMメモリーの変更・照会や機械語プログラムの実行ができますので、こんなときに便利です。

回路図の説明でも書きましたが、このRAMボードはRAMからの読み出しモード(0E2hの01hがON)の場合、PC-8001のN-BASIC ROMと空きROMをすべて無効にするため、PC-8001拡張CPUバスのROMDS0、ROMDS1、ROMDS2、ROMDS3信号線を基板上で短絡しています。

このため、ちくらっぺさん作 8kB SRAMボードと併用できません。同基板ではRAM有効化のためスライドスイッチでROMDS3信号線を強制的にGNDに落とす(Lレベル)にする仕様となっているため、この基板でROMDS0、ROMDS1、ROMDS2もLレベルになるため起動時にN-BASIC ROMが見えなくなります。(最初ハマりました ^^);; )

きらびぃさんデモをCMTでロードして動いた!

無事N-BASIC ROMの裏RAMとして動くところは確認できましたので、きらびぃさん作のデモをPC-8001にロードして動かしてみたいと思います。

最初の方で書いた配布サイトのデータを解凍するとwavデータが入っています。わたしはパソコンでwavデータを再生して、USBオーディオアダプタ経由でPC-8001とつないでカセットテープインターフェースでロードしました。なんと20分もある大作のデータであります。辛抱強く待つ必要があります。600ボーはツライw

待つこと20分、無事上記のようにデモ画面がスタートしました。PC-8001で64kバイトをフルに使った超大作デモです。PCG3声(わたしはPCG互換のロータスゲームボードの改造ですが)の音楽も素敵です。

みなさんも、PC-8001用メモリーボードを作ってぜひこのデモを堪能してください!!

(PC8001mk2をお持ちの方は、こんな苦労は必要ないわけですがw)

PC-8001無印用 128kバイトメモリーボードが無事動いたようなので(バンク切り替えのテストは未済ですが….)そのうちプリント基板化してみたいなぁと野望を持っています。いつかはきっと…

コメント