K68-VDG MC6847を使ったビデオボードですが、VRAMアクセスとVDGチップの競合がおきると画面にノイズが入ります。それをなんとかしたいと思っていたところをソフト的に対応してみた話をまとめてみます。

MC6847の描画ノイズ

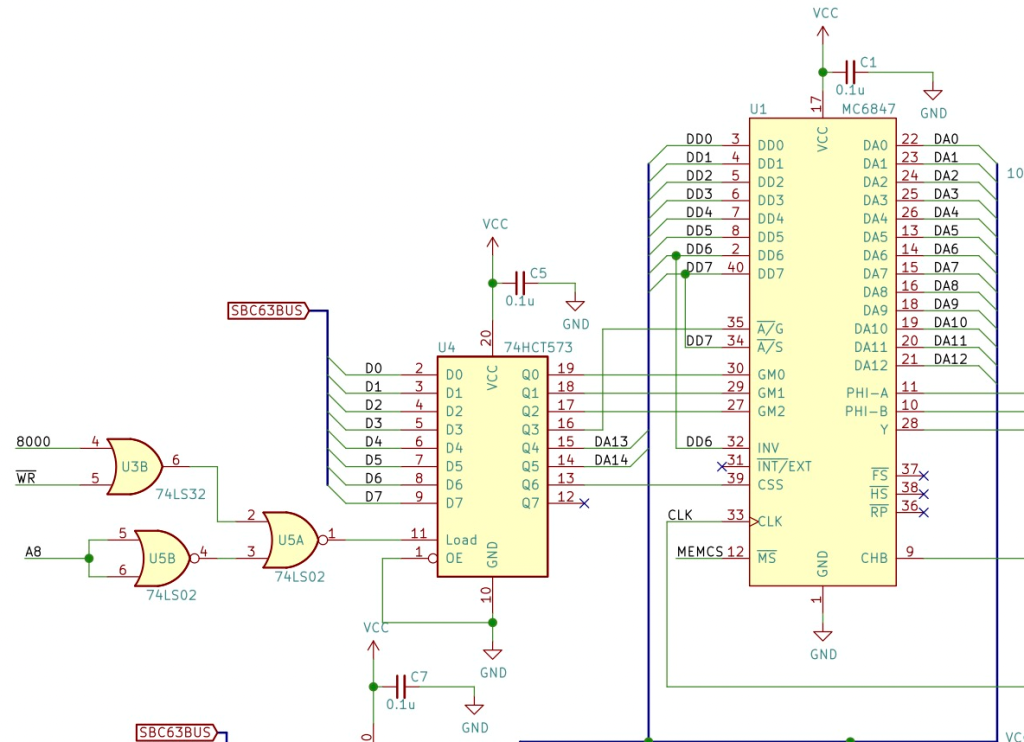

MC6847 VDGはアドレスデータを独自カウントしてVRAMに常にアクセスし表示データをスキャンしています。K68-VDGボードではMPU側からVRAMへアクセスする際にMS#端子をLレベルへ落とす操作をしてVDG側のアドレス信号をHiZ(ハイインピーダンス)にすることで競合が防げると思った設計となってます。しかし、これでは十分ではないようでして….

以下のBLOGでわたしのK68-VDGを作成しSBC6800と組み合わせてライフゲームを動かしていただいているryu10さんの記事がありまして、動作画面動画をYouTubeへUPしてくださってますが、描画の際にチラチラが目立ちます。

どうも、VDGとVRAM競合しないようにするには、HS#(水平同期信号)とかFS#(垂直同期信号)がLレベルであるタイミングにアクセスするのがお作法のようなのです。

もしくは、SBC6809Eにも搭載されているMC6883 同期アドレスマルチプレクサでMPUとVDGのメモリーアクセスを調停してやる必要があるようです。MC6883 同期アドレスマルチプレクサでは、VDG側からのアクセスをMPUのE信号がLのときに行い、しかもVRAMデータをラッチICでラッチすることでVRAMアクセス競合を防いでいる優れもののようです。

描画ノイズ対策

描画ノイズ対策として、過去のみなさまの作例はどうしているのかなぁと思ったら、ちゃんとMC6883を使用してVRAMアクセス競合を防いでいるか、HS#、FS#などの信号線をPIAなどに結線してソフトウェアでハンドリングする作例がありました。電子工作的に簡単なのは後者なので、今回は後者の「ソフトウェアでなんとかする」を試してみます。

SBC6303のI/OポートにVDGのHS#とかFS#信号をつなぐ

ソフト的対処のために最低限のハードの対処をします。今回はSBC6303を使いました。SBC6303は68系 40PバスにパラレルI/Oポートを持ってます。そのうち2つを使います。

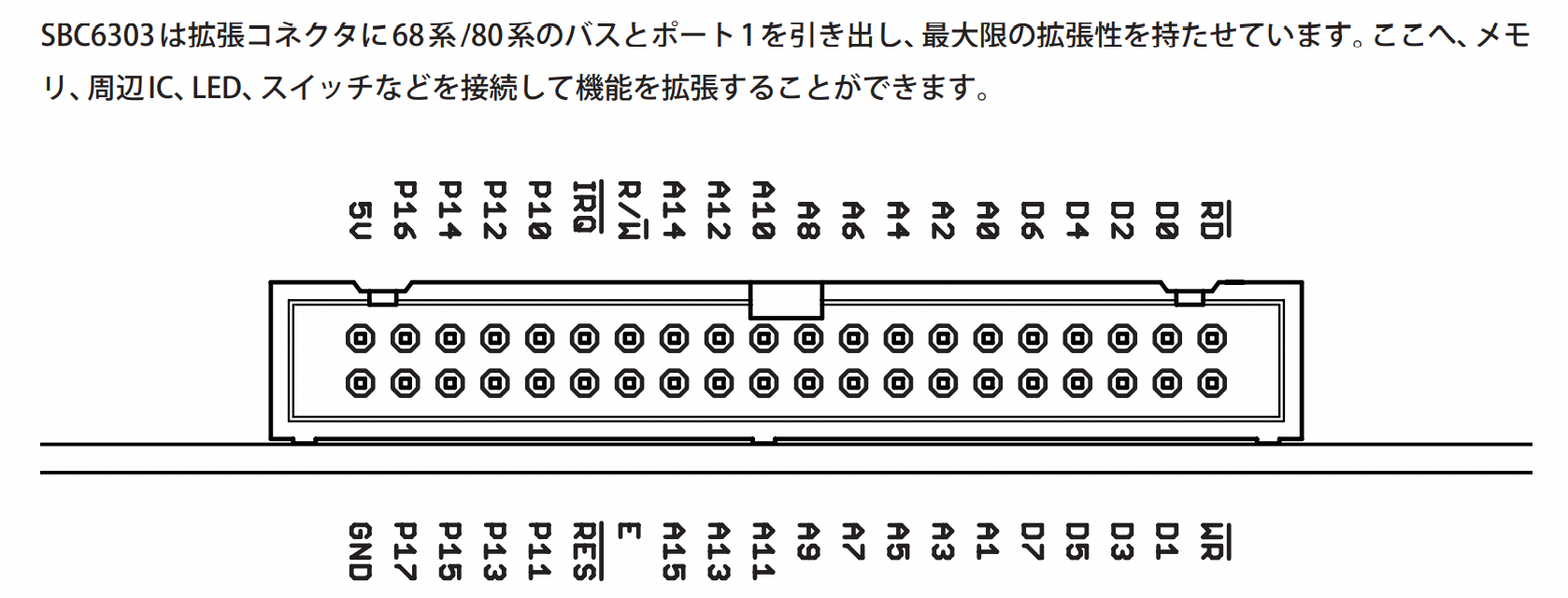

K68-VDGでは放置していたHS#(水平同期信号)とかFS#(垂直同期信号)のピンの状態を検知できるようにするため、前回の記事でも引用したSBC6303のバスは以下のようになってまして、HD63A03RP MPUのパラレルI/OがP10〜P17まで8本出ています。

SBC6303技術資料

Tomi9さんのSBC-IOとか、ryu10さんのSBC6802で上側のP10、P12、P14、P16は別の用途(アドレスでコード信号)で使われていたりしますので、今回は下側のP11、P13を使用しました。K68-VDG基板のMC6847 LSI のFS#、HS#端子から以下の写真のように2本ジャンパ線で結線します。

あとは、HD63A03RPで動かすソフトウェアでP11、P13ポートの状態を確認すると良いはず。

ryu10さんのライフゲームをちょっと手直し

ryu10さんのライフゲーム(K68-VDG版)のソースはgithubで公開されています。

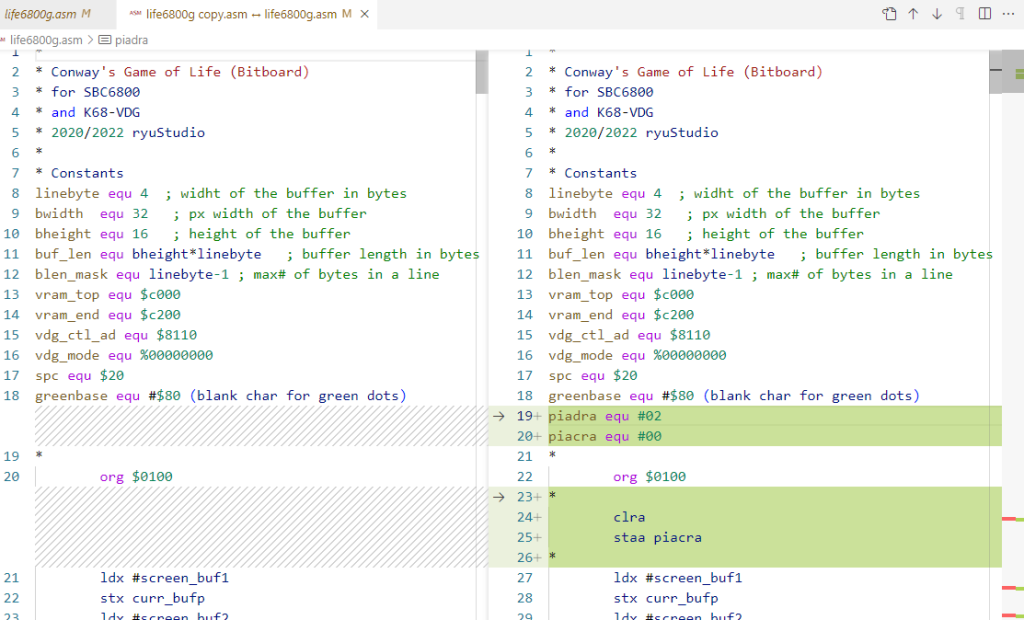

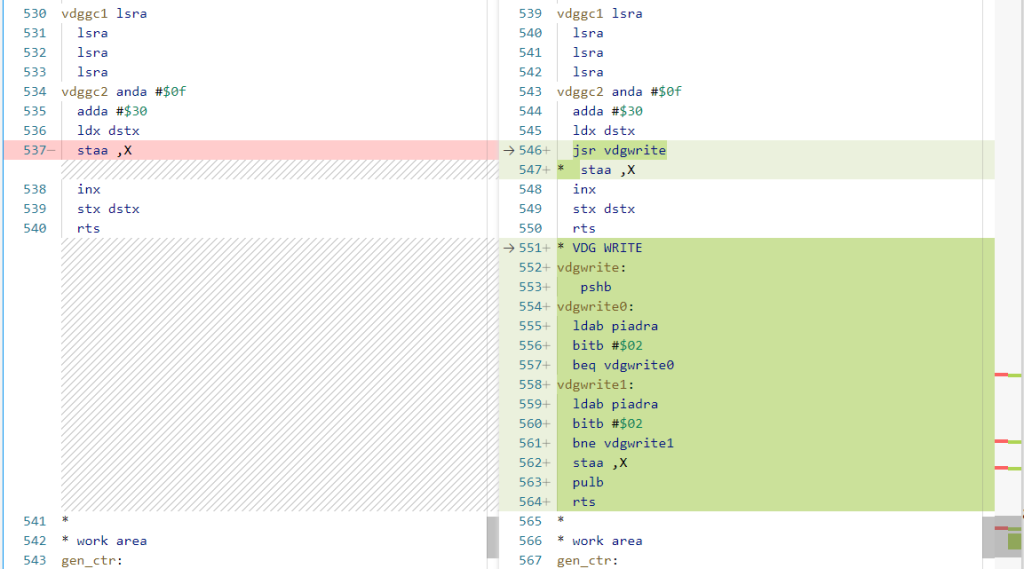

修正点ですが まずソースの最初のほうで、I/Oポートのコントロールポート、データポートを定義します。あと、念のためプログラムの最初でコントロールポートへすべてのポートを入力へ設定するため $00を出力。

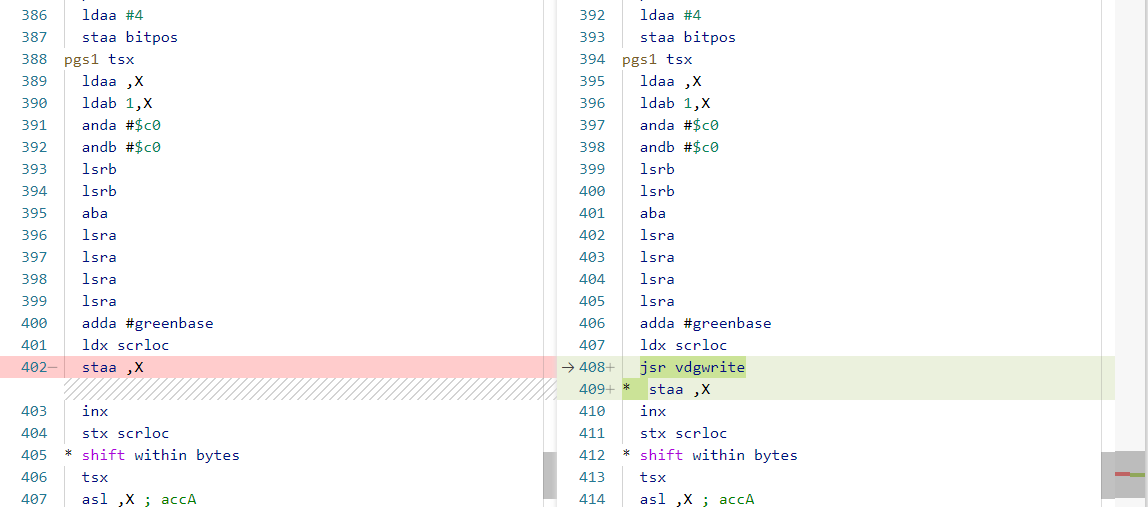

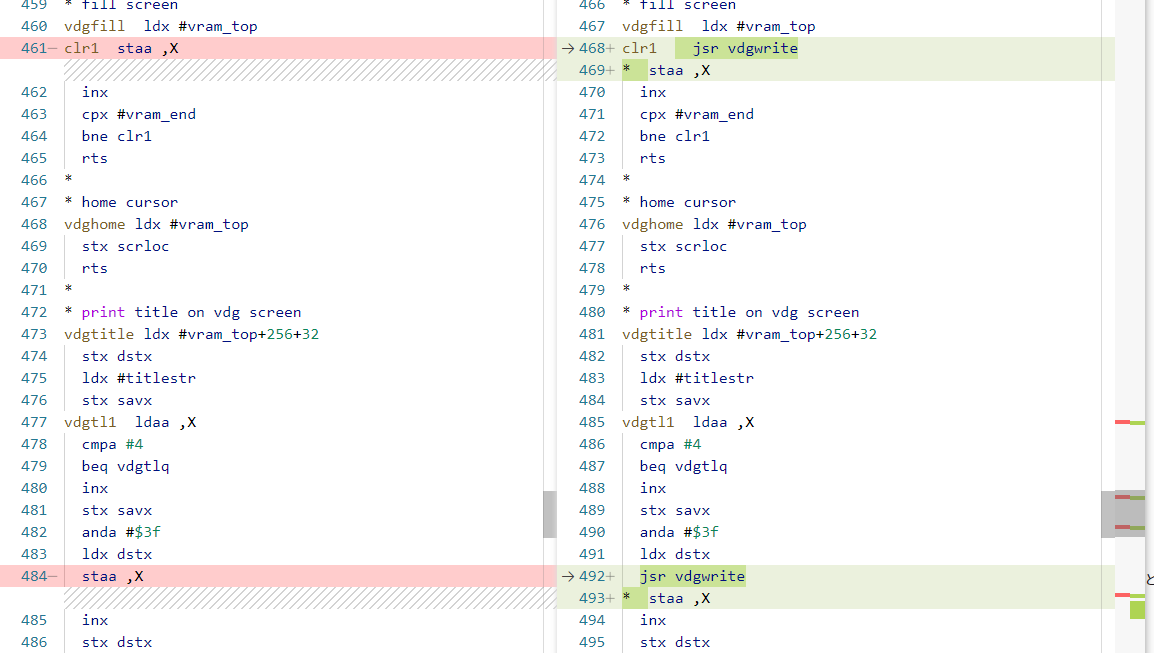

VRAMアクセスは “STAA ,X”というコードでインデックスレジスタ参照で、アキュームレーターにセットされたデータをストアしているようでしたので、このロジックをサーチしてVRAM更新サブルーチンコールへ変更。

VRAMアクセスサブルーチンでは、パラレルポートをチェックして HS#信号がLレベルになった瞬間にVRAMアクセスするようにプログラムを書き加えます。

`STAA ,X`でインデックスレジスタが指しているVRAMへアキュームレータに入っているデータをストアしてますが、その前段で $02ビットが Hレベル→Lレベルに落ちたのを見計らって実行するというロジックを追加しています。

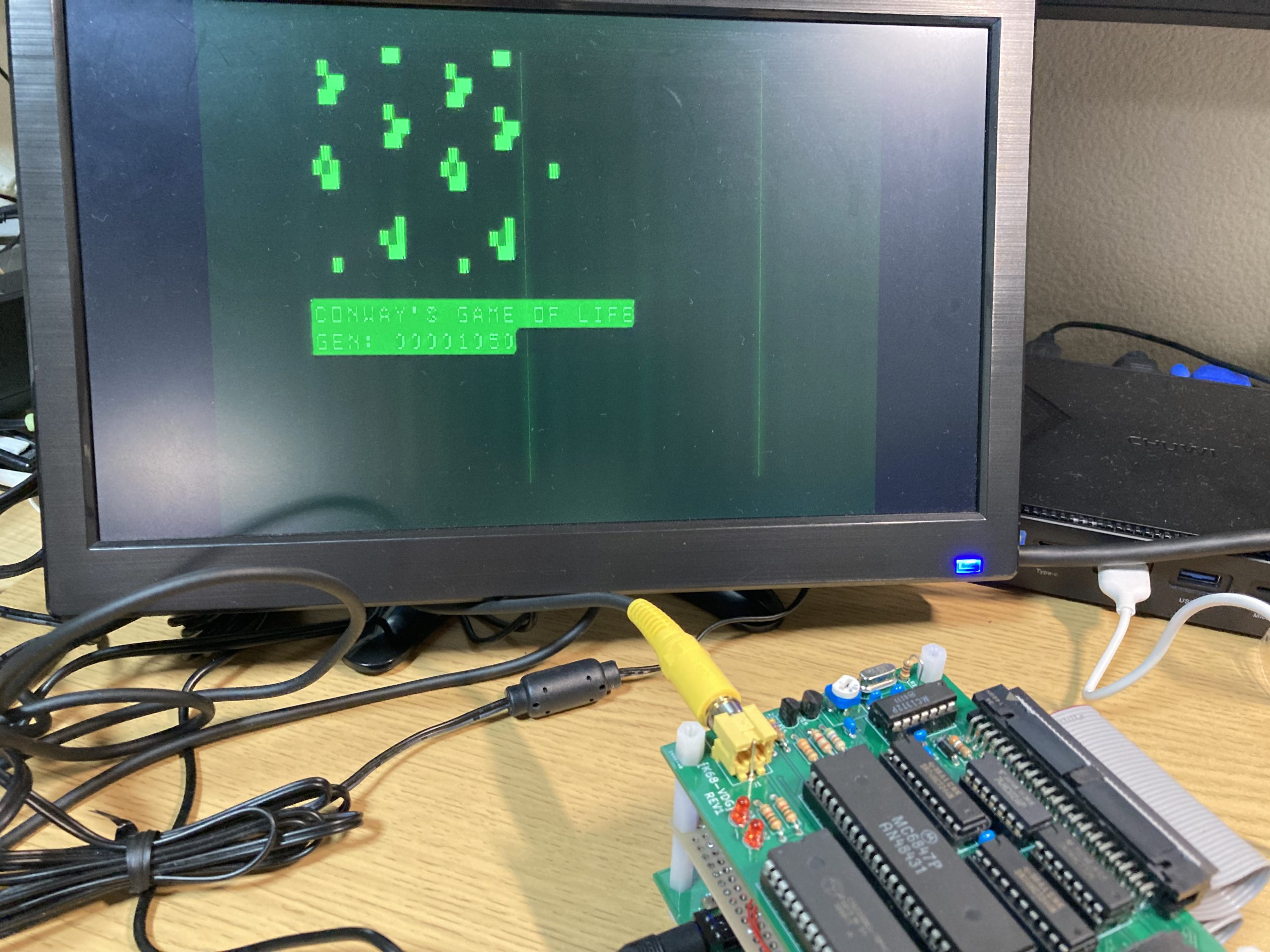

描画ノイズなしで動いた!

ちょっとだけのハード追加と、そのステータスをみながらVRAMアクセスするというソフト対応を実施したところ、ノイズが出ない綺麗な動きをするようになりました! やたっ!!

ソフトでいちいちチェックするロジックをいれるのが面倒ですが、ハードの改造がそれほどなくノイズ対策ができますのでオススメです。FS#(垂直同期)信号の方が2msecぐらい猶予があるらしいので、そちらでもっとまとめて書くとかのコードも挟んだりするともっと効率あがるかもです。今回はFS#信号はチェックしてないです。

将来的には 前回の記事でも書いたMC6883とDRAMを使ったシステムを構築して、VRAMにいつアクセスしてもチラチラしないVDGボードが作れたら良いなと思ってます。まだ先になりそうですが。

コメント