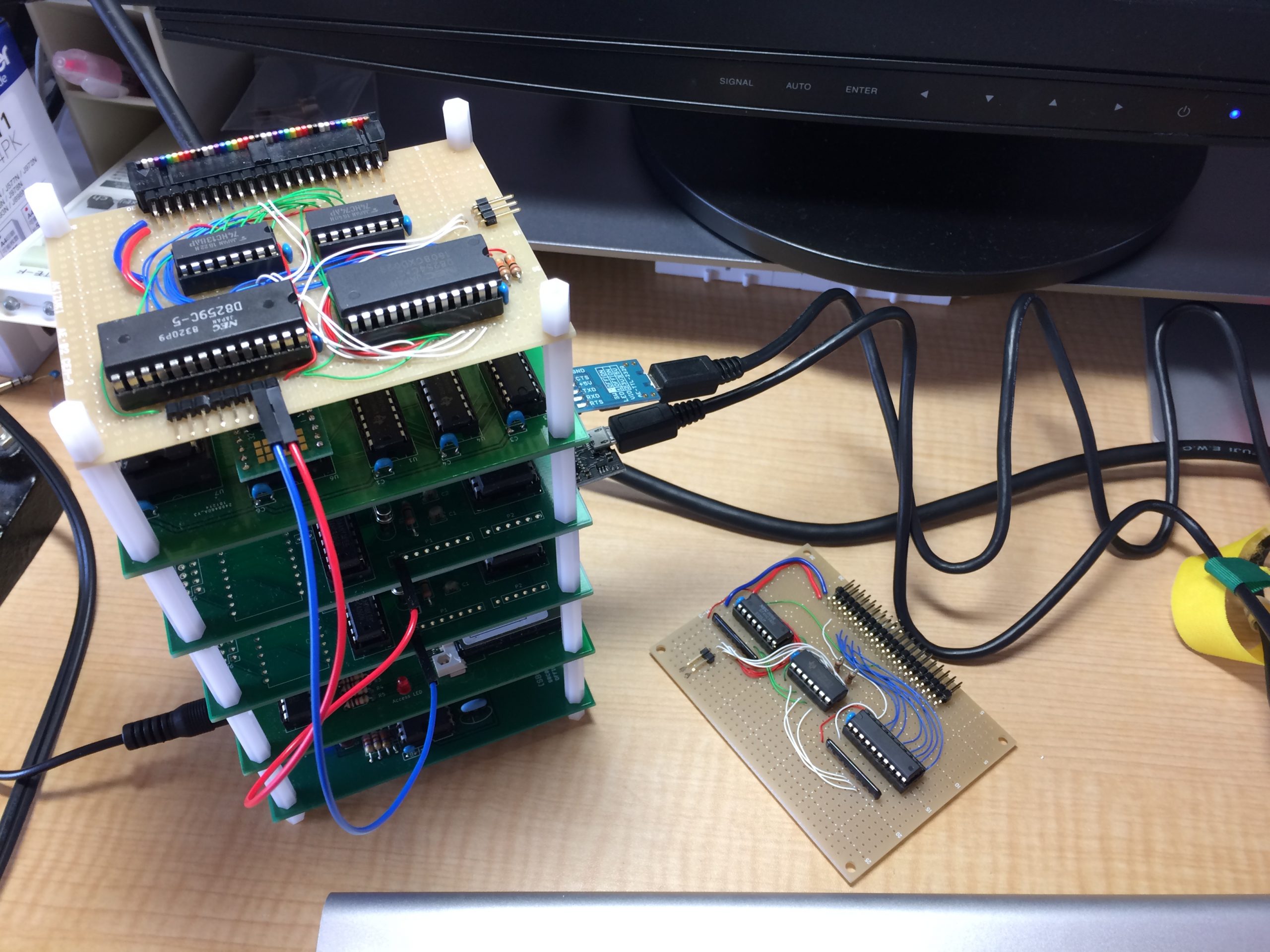

前回、80系割り込みコントローラー8259をSBC8080バスにつなぐボードを作りましたが、SBC8085とは正しく接続できるものの前々回のKZ80-CPUB(Z80 CPU)のINTA信号発生回路では割り込みコントローラー8259は正しく動作しませんでした。

8085CPUとZ80 CPUの割り込み動作の違い

Z80の解説本などの割り込みの章では「割り込み要求を受け付けた後、RST命令やCall命令をデータバスから読み込みます」という記載があるので、Z80と8080/8085の動作は同じだと思いこんでいました。

ところが、以下のz80.infoさんの資料(ザイログの資料っぽい)の3-132ページあたりを読むと…

http://www.z80.info/zip/ZilogProductSpecsDatabook129-143.pdf

要約すると以下のようなことのようです。

- Z80とインテル8080の割り込みモード0(ゼロ)の動きはフルコンパチではない。

- 8259割り込みコントローラーはINTA信号を3つ期待しているが、Z80は1回しか出さない。→これだとCall命令はCPUに渡るがCall先番地の2バイトの情報が渡らない

- 同じような動作をさせるとしたら、8080 CPUの動き(割り込みアクノリッジサイクル)をシミュレートしてあげる追加回路が必要。

割り込みモード0(ゼロ)は8080/8085 CPUとフルコンパチと思い込んでいたのでちょっとショックでした。^^)

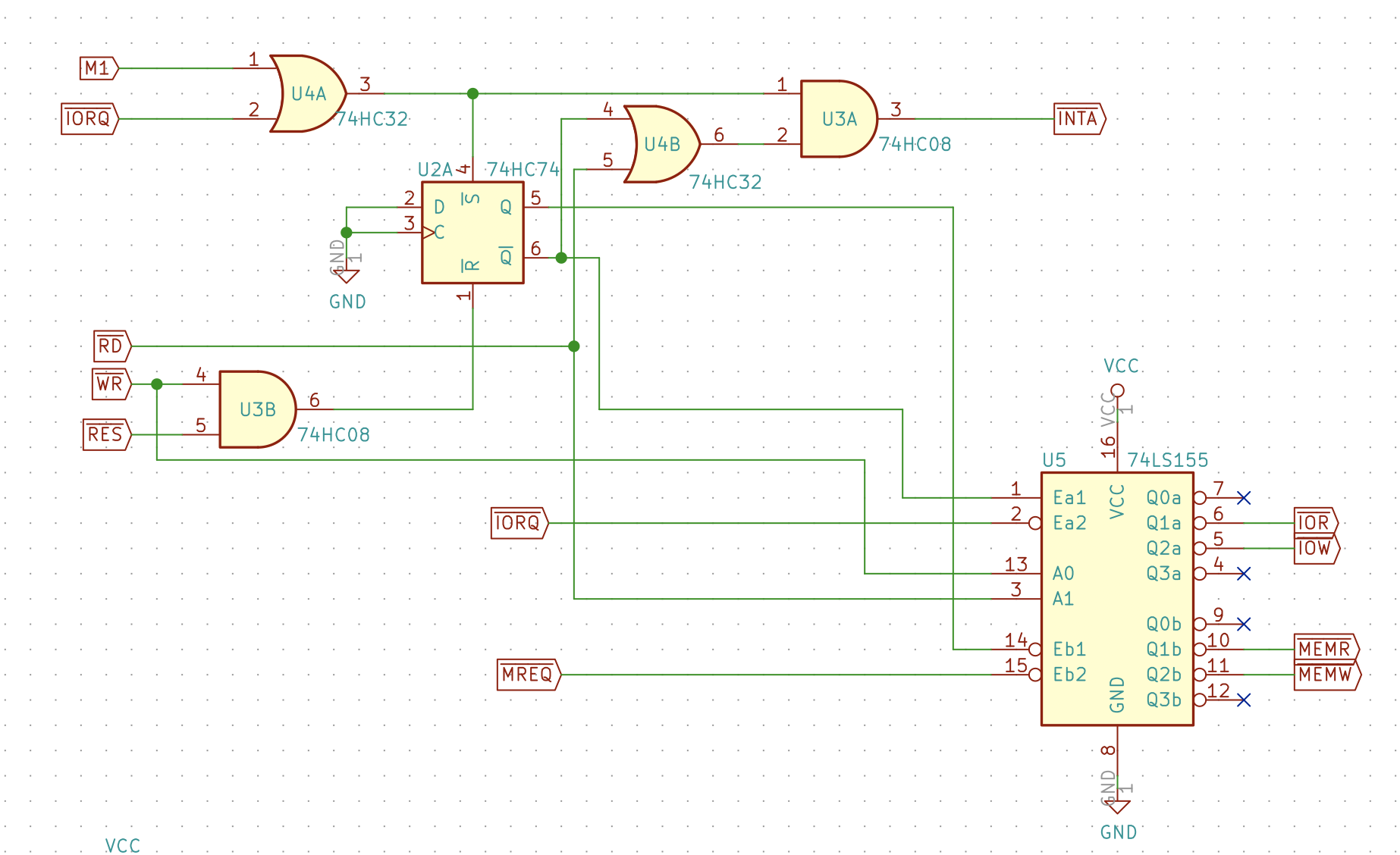

INTA信号追加回路

上記のz80.infoさんの情報にロジックICを組み合わせて作ったINTA信号追加の参考回路が出ていました。前々回のKZ80-CPUBへ追加した回路に更にICを3つ追加するとできそうです。ひとまずKiCADで回路図を引いてみました。

もともとINTA信号をつくるのにORゲート(74HC32)を追加済みでしたので、ANDゲート(74HC08)、Dフリップフロップ(74HC74)、DUAL 1-OF-4 DECODER(74HC155)があれば良い感じです。ちなみに元資料では74HC155(74LS155)の配線が間違ってる気がします…..

回路の説明もz80.infoさんの資料に出てましたが、わたしの言葉で意訳すると(間違ってるかも)こんな感じです。

- 割り込みアクノリッジサイクルにはいると、ORゲートでデコードされたINTA信号が8259へ届くと同時に、74HC74フリップフロップをセットします。(つまり、出力端子QがHレベル、QがLレベルの出力になります)

- つづくメモリー読み出しサイクルの際にこの回路で8259へのINTA信号が2つ出力されます。またメモリーへのRD信号はマスクされます。(これはHC155で止める形です)

- つづいてメモリー書き込みサイクルにはいりWR信号によって74HC74フリップフロップがリセット(出力端子QがLレベル、QがHレベルの出力になります)されて割り込みアクノリッジサイクルが終了します。(Call命令なのでスタックプッシュが続けて発動することに依存している模様です)

Z80は割り込み要求を受け付けたあとINTA信号(割り込みアクノリッジ)を1つだけ出すので、前々回のような1バイトのCall命令であるRST命令であれば問題ありませんが、Call命令の場合はCall先アドレスをメモリーから取得しにいく挙動になってしまうようです。本来は8259割り込みコントローラーからCall先を取得したいのでINTA信号(割り込みアクノリッジ)を2つ出すように工夫した回路になっているということのようです。(メモリー読み出し信号をINTA信号(割り込みアクノリッジ)へ変換している)

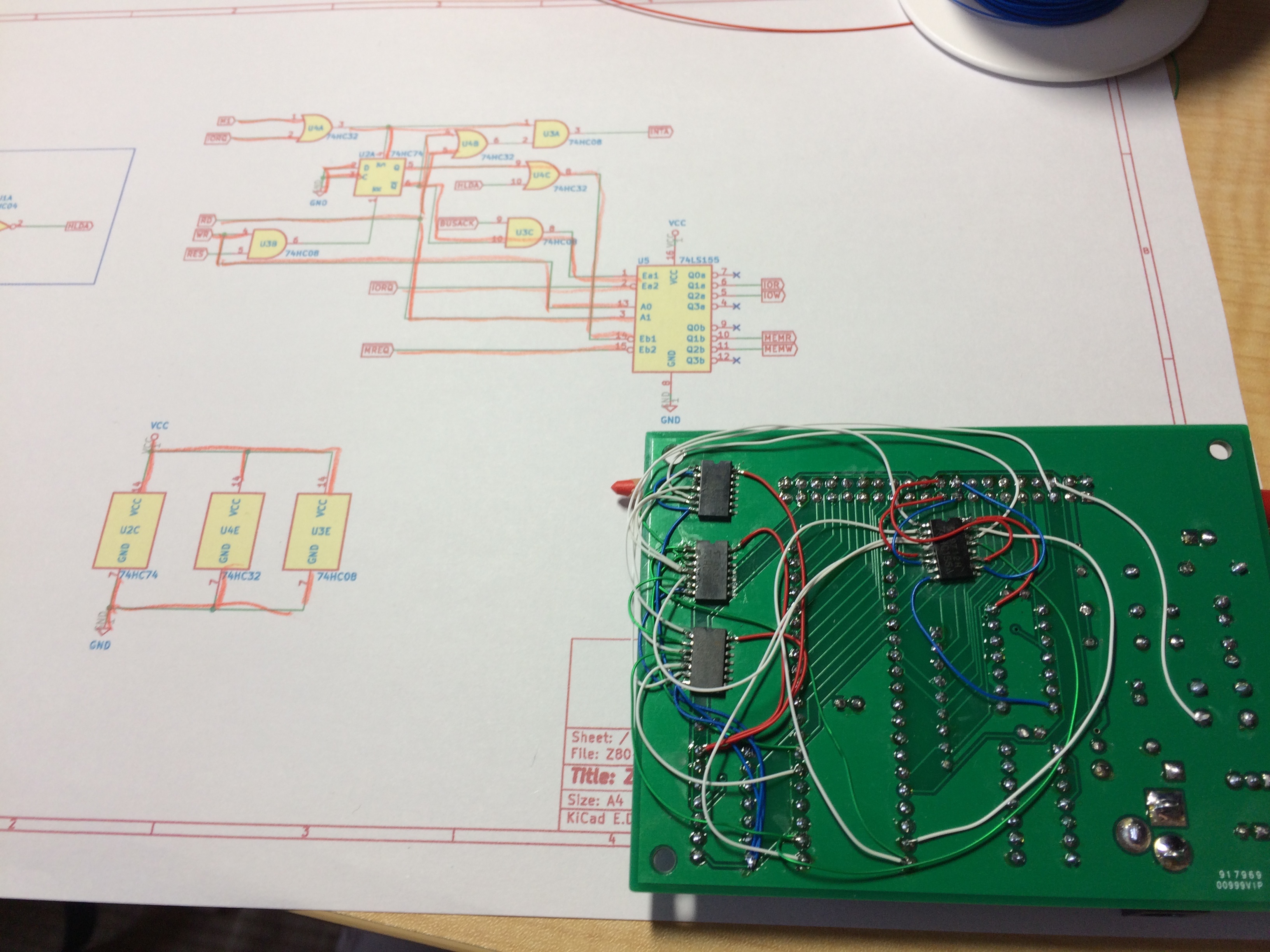

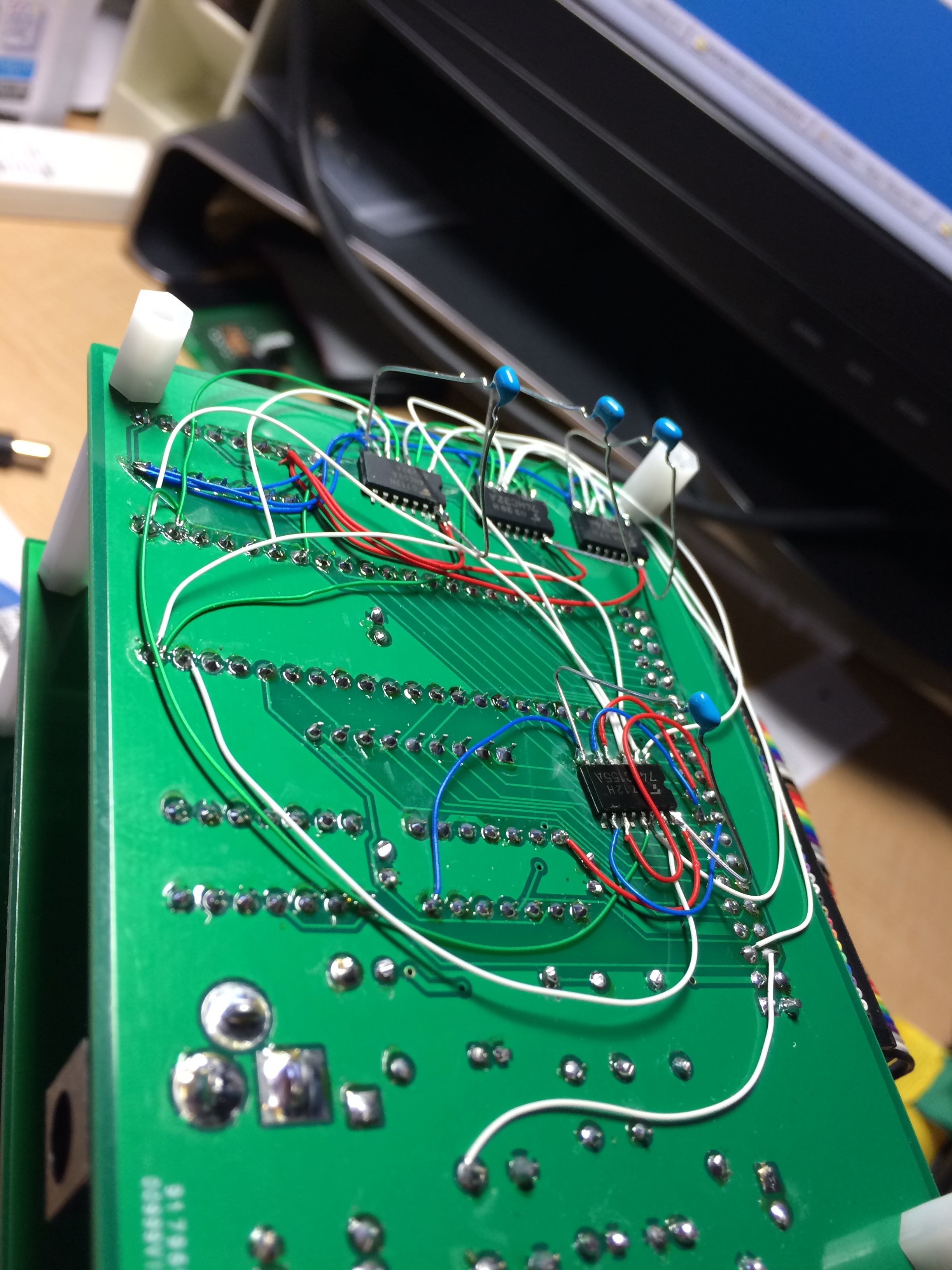

試作してみた

前々回のKZ80-CPUBの裏側に74HC32 SOP(表面実装)タイプICを瞬間接着剤wではりつけたものに、追加で3つのICを貼り付けて回路図通り配線してみました。

実は、はんだ付け不良に気づかず一発ではうごかなかったのですが….

最終的にははんだ付け不良箇所をしっかりつけなおして安定稼働させることができました!!

KZ80-CPUB REV2を3月に発注したあとにこの事象に気づいたため、githubにあがっている リリース2.0 の回路図、プリントパターンは8259割り込みコントローラーでは動かず、ロジック回路版の割り込みコントロール回路(RST命令出力)にしか対応していないのでした。近日REV2.1を作成する際にはこの回路を取り込もうと思います。

コメント