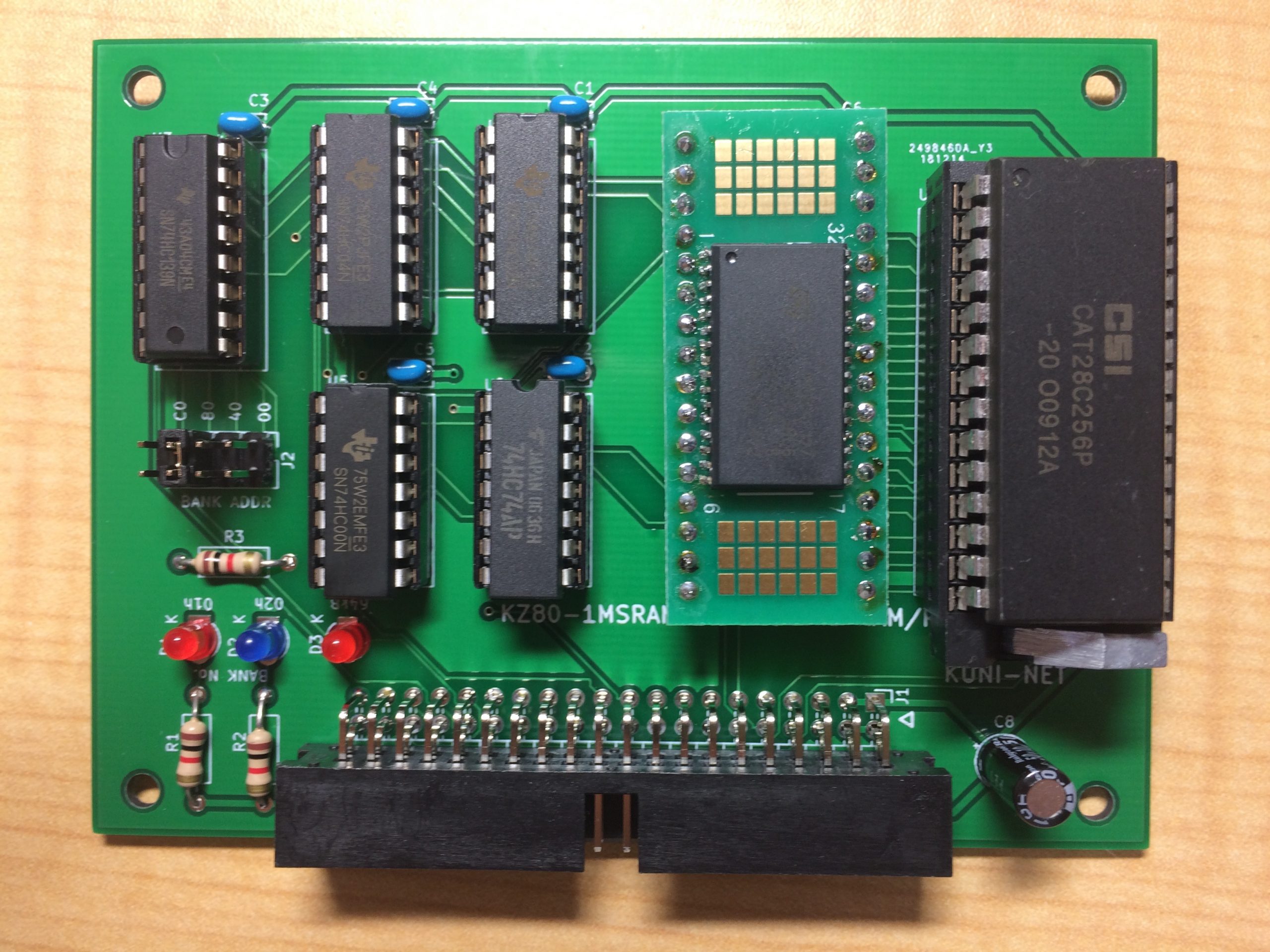

KZ80-CPUBやSBC80系のCPUボードとSBC8080バスでつながって動作する128kB SRAM&ROMボード KZ80-1MSRAMのREV2を作りました。

基板データ等配布先について

いつもどおりREV2に関するKiCADデータや関連ソフトウェアはgithubで公開しています。以下をご覧ください。

https://github.com/kuninet/Z80_1MRAMB/releases/tag/2.0

ちなみに、バンク切り替えイメージなどまとまった解説はgithub wikiに書いています。そちらも併せてご覧ください。

https://github.com/kuninet/Z80_1MRAMB/wiki

REV1からの改良点

REV1からの改良点は以下のとおりです。

- 起動時、リセット時に初期バンク番号を バンク1へ固定

- REV1では起動時、リセット時にメモリーバンク番号が不定でした。これは設計当初から固定RAM域(4000h-7FFFh)をあてにして機械語モニターを起動させ、ソフトウェアで初期バンク番号を決定するという方式を考えていたためです。

- この方式だと、機械語モニターへ命令追加しないとCPUボードによって初期バンク番号が違ってしまうという状態でした。

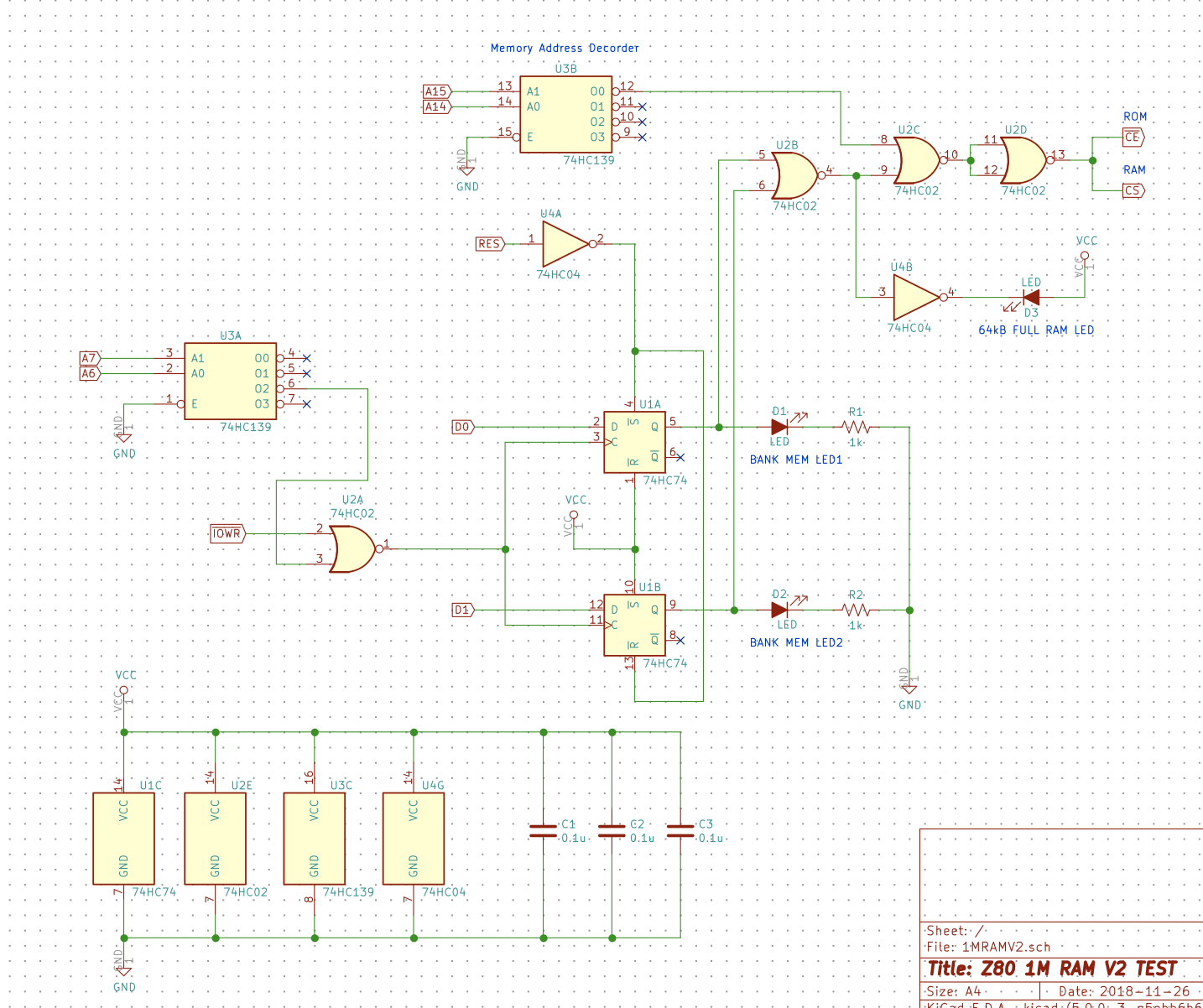

- そこで、メモリーバンクレジスタのICを74HC573(Octalラッチ)から74HC74(D-FF)へ変更しました。実験回路として検討したときの回路図は以下になります。

- CPUリセット信号パルスを74HC74のDフリップフロップのリセット/セット端子へ与えることでメモリーバンク番号 “01”に初期設定されるようにしています。

- 64kB フルRAM切替回路

- いままでバンク0の指定はバンク01に読み替えることで意味がないものでしたが、そこを見直して64kB切り替えの指定としました。

- 動作原理としては、上記 回路図のメモリーバンクレジスタの出力が “00”(つまり両方Lレベル)となった際の信号と、ROM/RAM選択の74HC139デコーダの信号をあわせてROM/SRAMの#CEへ供給することでフルRAM化を実現しています。(バンクレジスタが00だとSRAMしか選択されなくなります)

- フルRAMに切り替わったことを確認できるようにLEDも追加しました。(バンク0=フルRAMなので無用かもですけど….^^)>)

- バンクレジスタI/Oアドレス選択ジャンパ

- いままでバンクレジスタのI/Oアドレスは80h固定でしたが、ジャンパにより00h、40h、80h、C0hの切り替えが可能となりました。

- 基板スペース等の関係でアドレスデコーダを74HC138にできなかったのが心残りですが….

今後について

リセット時のRAM構成がハード的に安定したことと、フルRAM切り替え回路が作成できたので、CP/Mを動かしてみたいと思います。参考にするのはいつもお世話になっている以下のGrant氏のページです。

Grant's home-designed CP/M machine

コメント

[…] 128kB メモリーボードで64kBフルRAM化が可能となったので、SBC8080バスにつながるコンパクトフラッシュボードを作成してCP/M 2.2を動かしてみたいと思います。 […]