前回のSBC68系バスとSBC80系バスの変換ボートの記事でも書きましたが、どうも6502CPUマイコンのSBC68系バスに8255A PPIをぶら下げても思ったように動いてくれませんでした。今回、いろいろとブレッドボードでトライしてみましたというお話です。

68系CPUマイコンと8255PPI

ネットをいろいろとさまよっていると、68系CPUに8255A PPI(パラレルI/O LSI)をつないでいる方がいらっしゃいます。以下の方はHD6301と8255A PPIをつなげておられます。

RD/WR信号のデコード方法もE信号(6502CPuだとφ2)とR/W信号のNANDを取っていたりしてですね、わたしの6502CPUマイコンとほぼ同じ回路。ちょっと違うのは、RD/WR信号を直接PPIにつないでて、CE端子にはアドレスデコード信号を直接つないでます。

前回のバス変換基板だと、A15〜A8の上位アドレスデコード信号と RD/WR信号を 74HC139で合わせていたりするので遅延が発生しそうというあたり…

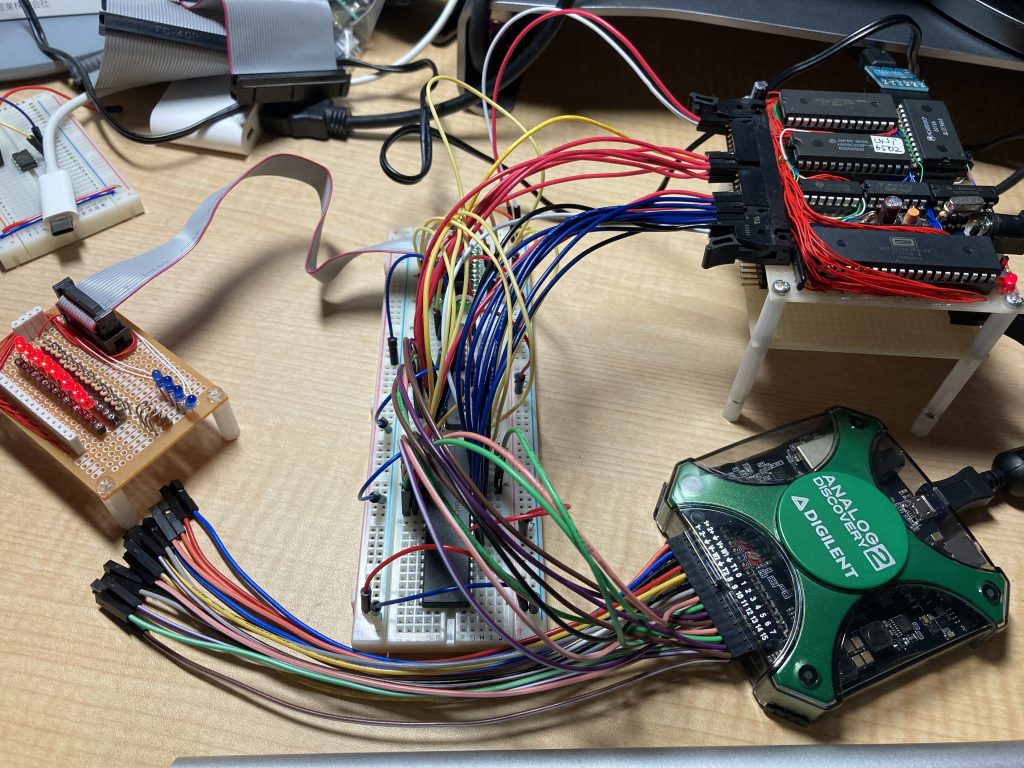

ブレッドボードで組んでみた

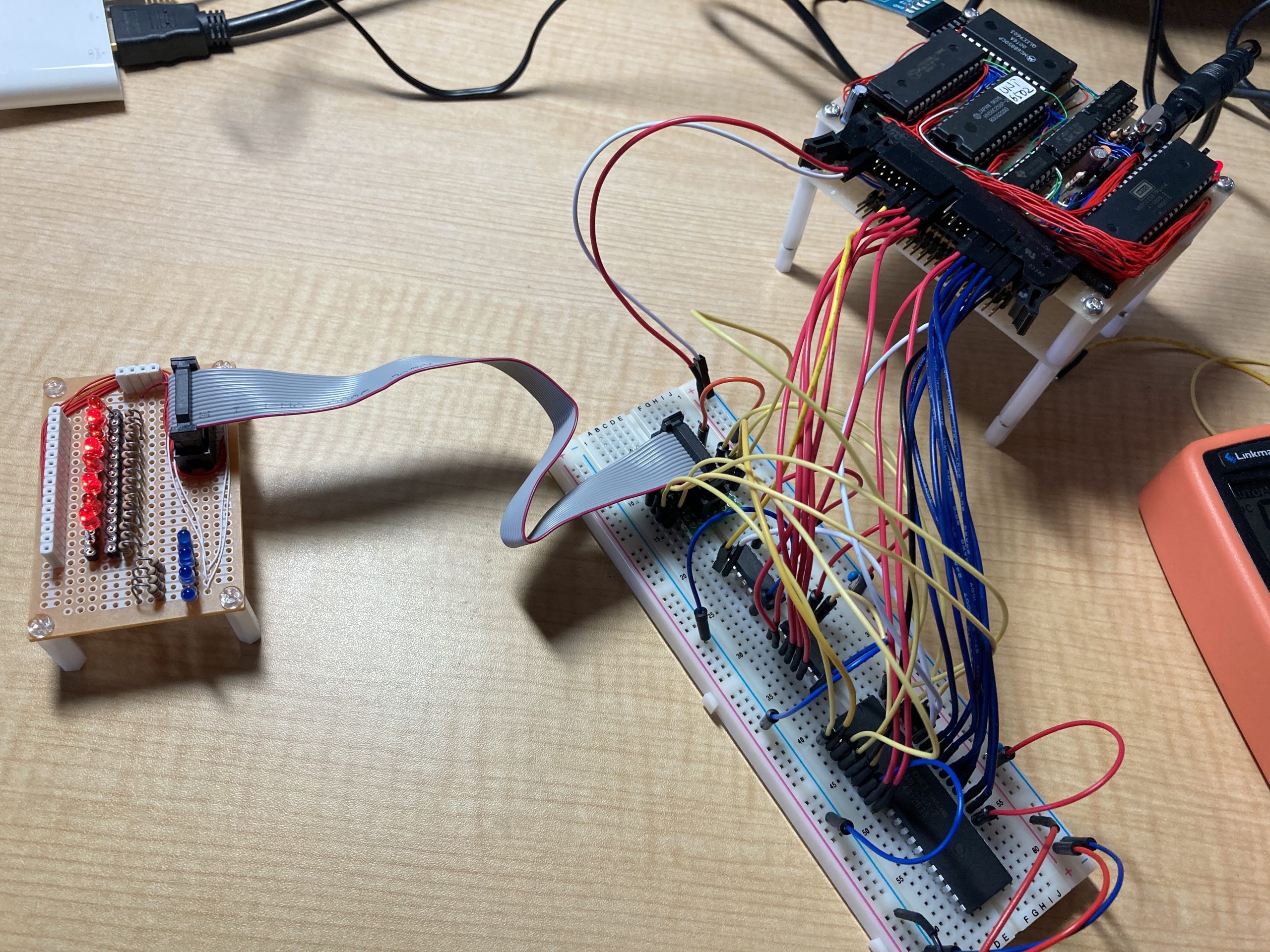

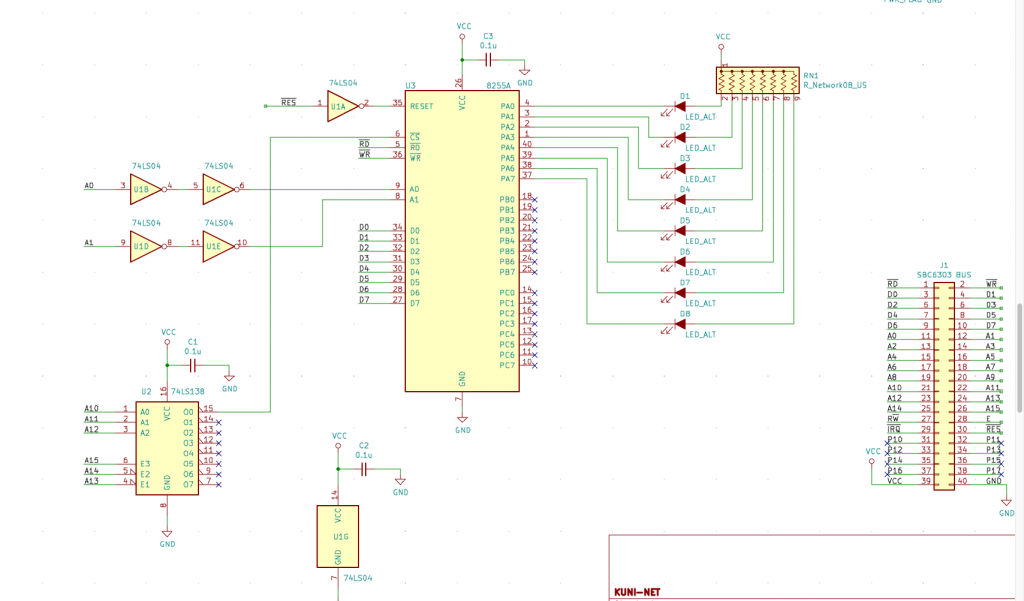

6502CPUマイコンのバスと8255A PPIをつなぐ同じような回路をつくってみました。回路はシンプルですがこんな感じです。これをブレッドボードで実装してテストしてみました。

8255A PPIのアドレスデコードはメモリーマップドI/Oで$8000〜8003番地です。$8000番地がポートAのレジスタで、$8003番地はコントロールレジスタ。

Universal monitorで$8003番地にいつもの初期化パラメーター$80を投入して全ポートOUTPUTにすると全ポートがLレベルに落ちまして、LEDが点灯しました!

気を良くして$8000番地に$55とか$AAとかLEDが歯抜けになるデータを出力したところ、$8002とか$8003番地が更新されたりします。なぜ2番地が更新?!

上記回路ではアドレスはフルデコードしていないので、$8004番地に$8000番地のポートA用レジスタのイメージが出てきまして、そこに$AAとか$55とかを出力すると$8000番地も更新されて 8255A PPIのポートAにつないだLEDがいい感じに点滅したりします。アドレス指定の挙動が不安定です。

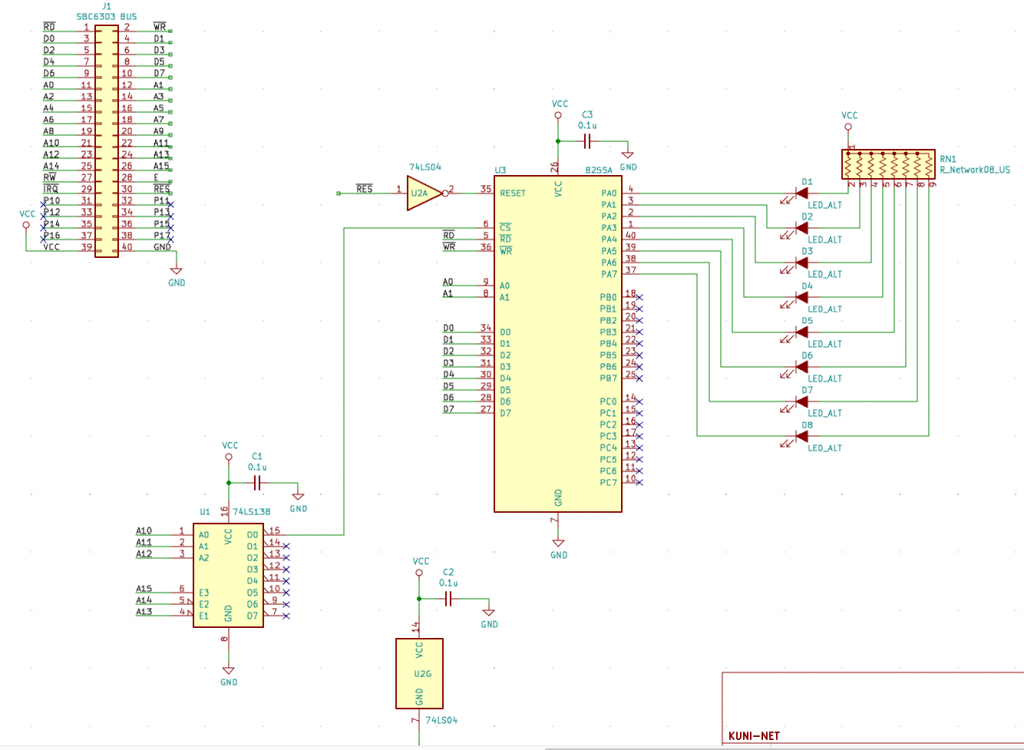

8255Aへ出力するときのタイミングチャート

いまさらですが、8255Aのデータシートをみますとデータ書き込みの際のタイミングチャートとしてはこんなタイミングを想定しているようでした。

uPD8255A Datasheet

WR信号がLに落ちる前のアドレスバス信号(A0,A1)のセットアップタイム tAWは0nsec、WR信号がLレベルからHレベルに上がったあと最低20nsec(tWA)はアドレスバス信号の保持が必要。

データバス信号の方は、WR 信号がLからHに戻るまで最低100ns(tDW)は必要。WR信号がLレベルからHレベルに上がったあと最低30nsec(tWD)はデータバス信号の保持が必要。

最初の8255は WR信号がLに落ちるところで反応していた模様ですが、8255Aになってから8085の動きに対応するためL→Hに変化する後半あたりで反応するように変更になった模様です。以下のページに詳しいお話がでてました。

8080では書き込み時にデータバスに出力されたデータが確定してからWR*ストローブパルスが出力されました。したがって、WR*ストローブが有効となる時間には書き込みたいデータが確実に入力されています。ところが、8085になると、Z80-CPUなど他の多くのプロセッサと同様にWR*ストローブが出力された後に少し遅れて有効なデータがプロセッサから出力されます。WR*ストローブの終端時には十分なセットアップ時間を確保したうえで確実なデータが周辺LSIやメモリに与えられます。後者のほうがアクセスタイミングに余裕を持たせやすいため、広く使われる傾向があります。

半導体コレクション展示会場〜USART, PPI, PIC

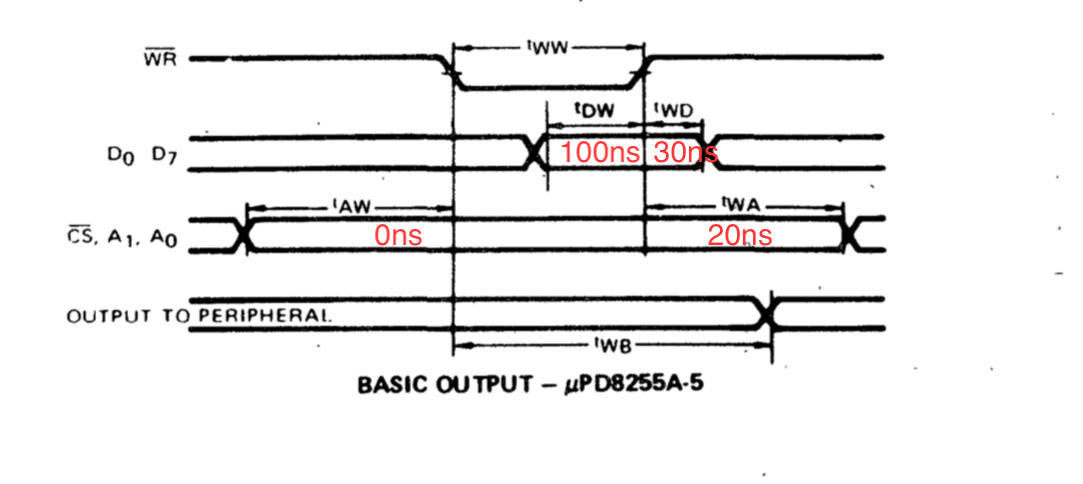

ロジアナで見てみました

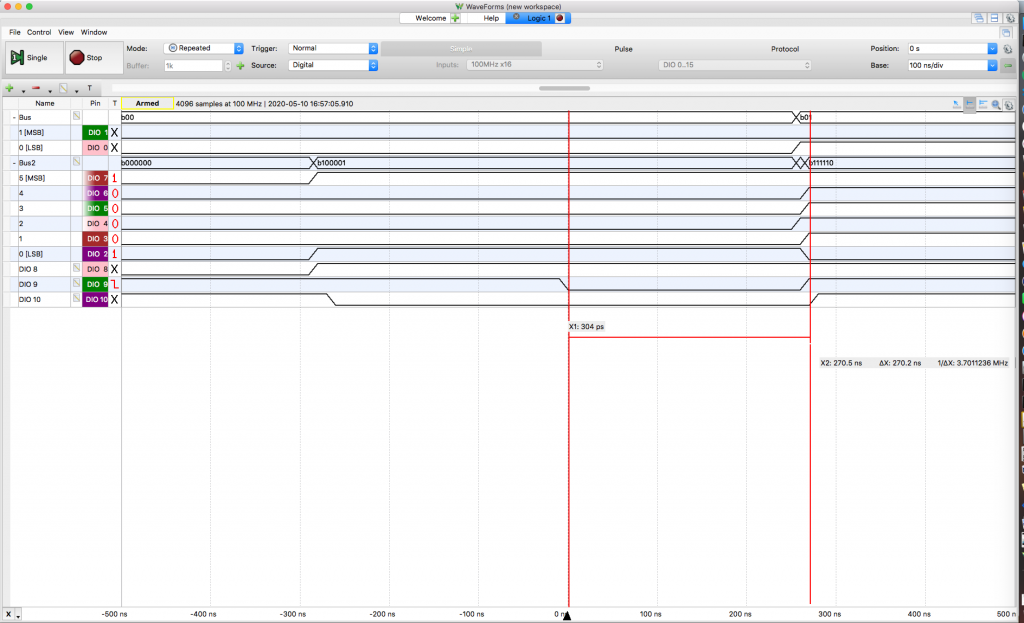

回路をいくら睨んでもさっぱりわからないので、ロジアナで8255A PPIへ書き込みしたときの信号を観測してみました。

上記の図で、DIO(デジタルI/O)0番,1番はアドレスバスA0とA1です。DIO8がRD、DIO9がWR、DIO10は8255A PPIのCEです。

データバスは観測してませんが、実機で動かしたときにアドレスはズレますがデータは正しく入っていたので許容範囲に入っていると勝手に思ってました。

波形を見ると WR信号が立ち上がったとたんにアドレスバスA0,A1信号が変化しています。8255A PPIが期待しているアドレスバス信号の保持はされていません。

6502CPUはφ2クロック信号によって動作しますので次のメモリーアクセスのため信号が遷移している模様。Z80などよりは厳しい信号遷移となっている気がします。これだと8255A PPIが書き込み命令を受けて該当のレジスタを更新しようとしたらアドレスバス信号がズレているということになってしまっているように見えます。

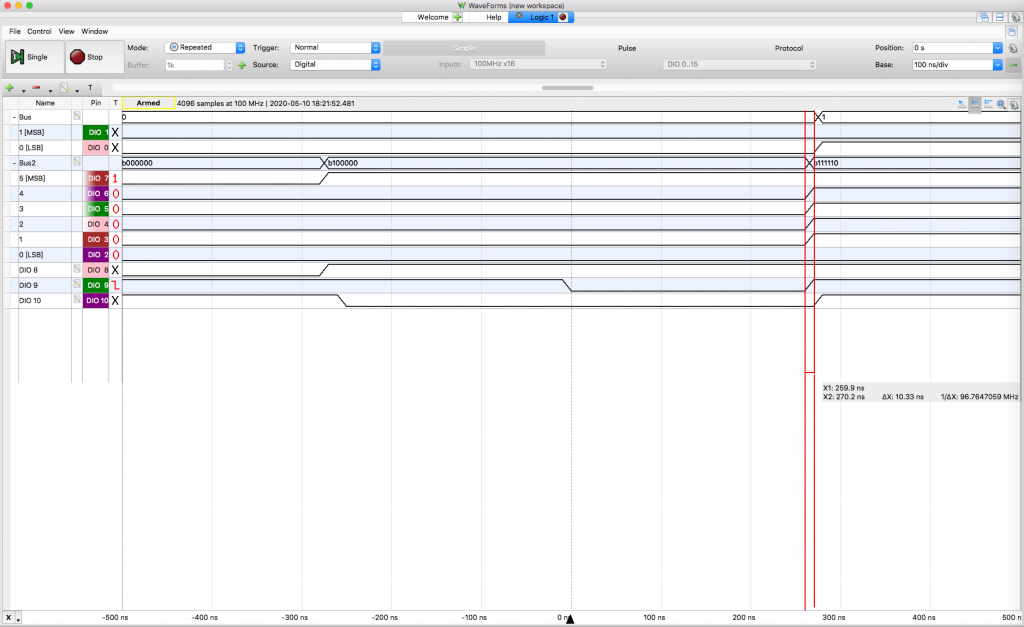

A0、A1信号をちょっと遅延させてみた

今回リセット信号のために74LS04のNOTゲートを使用していて、6つのゲートのうち5個余っていました。そこで、アドレスバスA0、A1信号をNOTゲート 2つを通してちょっとだけ遅延させてみたらどうだろうと思いつき、以下のような回路へ変更してみました。

TMS9918ビデオボードの参考回路も、DRAMからSRAM対応のためにNOT回路x3つを通した回路があったので、真似してみました。

波形を見てみると WR信号の立ち上がりのあと、ちょっと短いですが10nsecぐらいはA0,A1のアドレス信号が保持されるようになりました。

この対応のおかげで、$8000番地にデータを書き込んで$8002番地とか$8003番地にズレて書き込まれるなどの謎事象は解消してLEDのチカチカ動作を確認できました!!

この対応が正しいかというと….

ひとまず6502CPUマイコンで80系の8255A PPIパラレルI/O ICがコントロールできました。8255A PPIは動作タイミング的には厳しいので、やはり68系のMC6821とか、純正の6522/21などを使うのが安心ではないかというのが感想でありました。

そのうちW65C22 VIAあたりを入手して使ってみたいなぁと思ってます。ただ、国内の部品販売店で気軽に買えるところがなくて…

コメント