Z80/8080 CPU用に128kB メモリーボードを作成して動いたので、次はSBC68系の128kB メモリーボードを作ってみたいと思います。

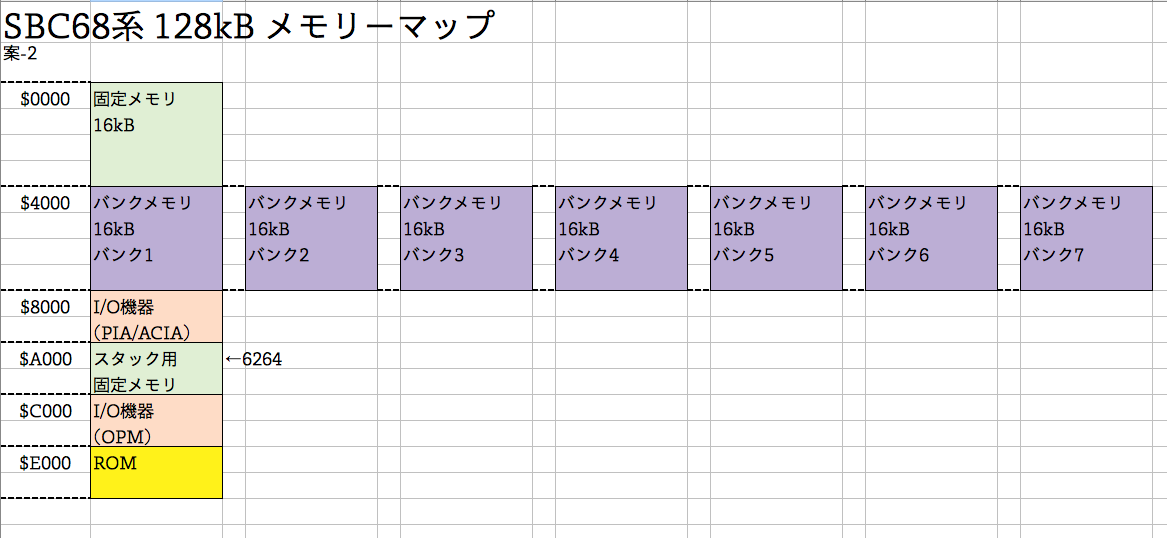

メモリーマップの検討

SBC68系はZ80/8080系と違ってメモリーマップドI/O、つまりメモリーアドレス上にI/O機器がつながっています。

伝統的に$0000〜$7FFFまではRAM。$8000台はI/O、$A000はスタック用RAM、$E000〜とか後ろの方はブートベクタの関係もあってROMにするのが通例です。

当初はPIAやACIA、自分で搭載したFM音源チップなどをすべて$C000台持っていってメモリー領域を確保するという案も検討しましたが、それだとSBC6800/SBC6809の基板にパターンカット等を実施する必要がありちょっとポリシーに反する感じ。以下の方針としました。

- 固定RAM領域は $0000〜$3FFFの16kBとする。(もともと8kBなのでこれでも余ると思いました)

- バンクメモリは $4000〜$7FFFの16kBで、7バンク準備。(ここまで128kB SRAMを使用)

- $A000からのメモリー領域をオリジナルのMIKBUGや電大版BASICがスタックとして使っている(MC6810想定)のため、余ってきている8kB SRAMを配備することにする。

メモリーマップのイメージはこんな感じです。

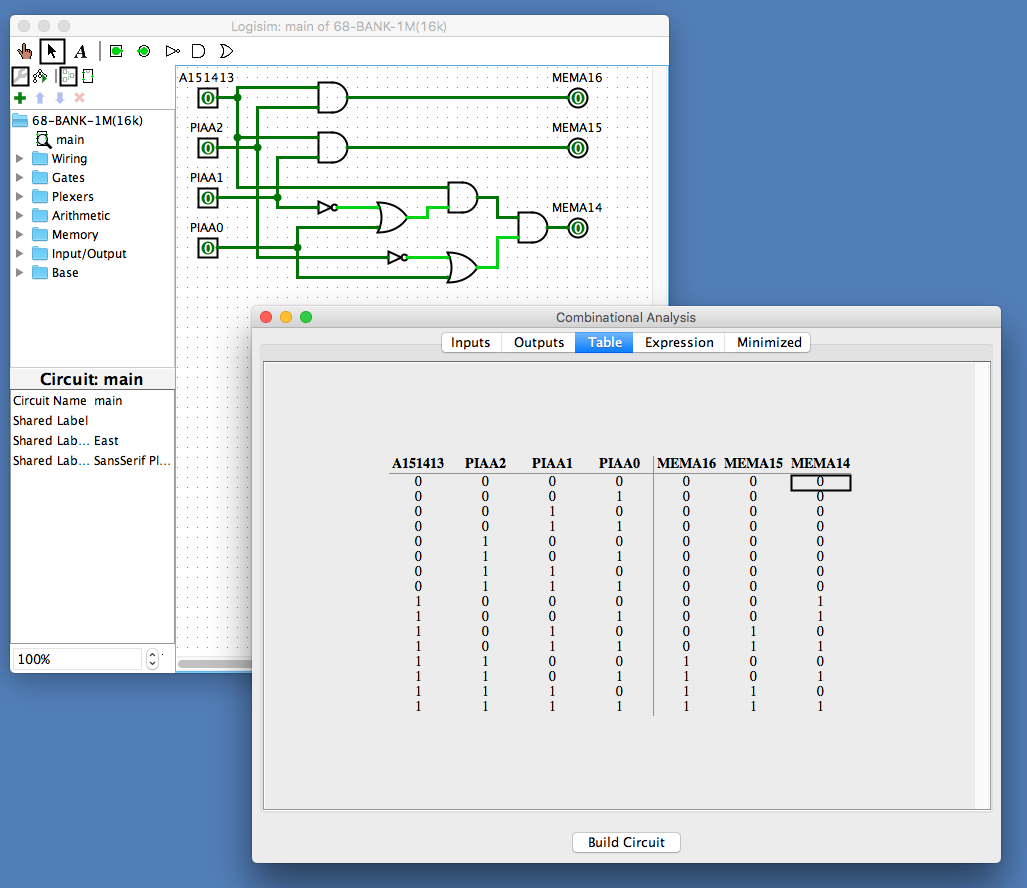

バンク切り替えコントロール回路

固定RAM領域($0000〜$3FFF)と バンク切り替え領域はどちらも同容量(16kB)としましたので、128kB SRAMを8分割して使用することになります。よって前回と違ってメモリーの3本のアドレスバス信号線(A14、A15、A16)をうまいことコントロールすることにします。

またバンクレジスタ機能は今回はSBC6303のI/Oポートによってコントロールすることにします。(独自のラッチは作りません)

- CPUが固定RAM領域($0000〜$3FFF)にアクセスする場合はバンクレジスタの値に関わらず A14=A15=A16=”L”とする。

- CPUがバンクメモリ領域($4000〜$7FFF)にアクセスする場合は、バンクレジスタの示すアドレスを使用する。

- ただしバンクレジスタに0(ゼロ)が設定されている場合は デフォルトのバンク1(A16=A15=”L”、A14=”H”)とする。

上記を満たすロジック回路を、今回もLogisimを使って2入力ゲートICでシミュレートしてみました。

ゲートIC x3で実現できそうです。

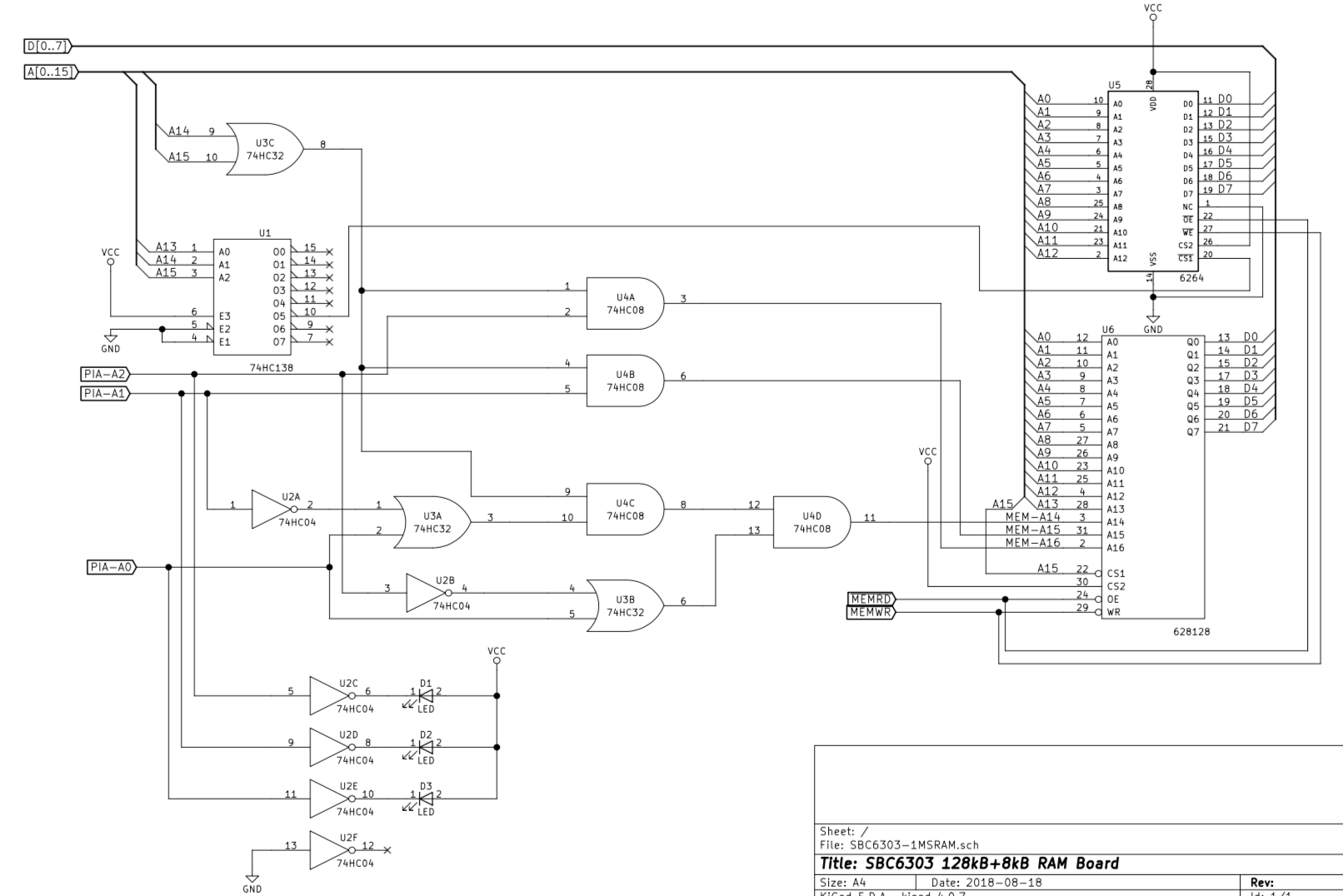

回路図の検討

バンクメモリなどのコントロール回路が決まったので、128k SRAM、8kSRAMをコントロールする回路図を書いてみました。

- 128kB SRAMの CS1へはアドレスバスのA15を入れます。$0000〜7FFFまでのアドレスならA15=”L”なので…(CS2はVccへ)

- 8kB SRAMの CS1にはA13、A14、A15を74HC138でデコードした線をつなぎます。(こちらもCS2はVccへ)

- バンク切り替えコントロール回路へは SBC6303のI/O出力 P10、P11、P12ピンを接続。アドレスバス A14、A15をORゲートを通して 両方”L”のときに”L”を出力させてつなぎます。(74HC138のデコードの代替です)

- バンク切り替え状況が目で見てわかるように SBC6303のI/O出力 P10、P11、P12ピンにNOTゲート経由でLEDを接続します。

実は….

実は上記の回路図は修正して正しく動いている(と思う)版です。

基板作成当初の回路図では何を勘違いしたか固定RAM領域のデコード部分が間違ってました…orz

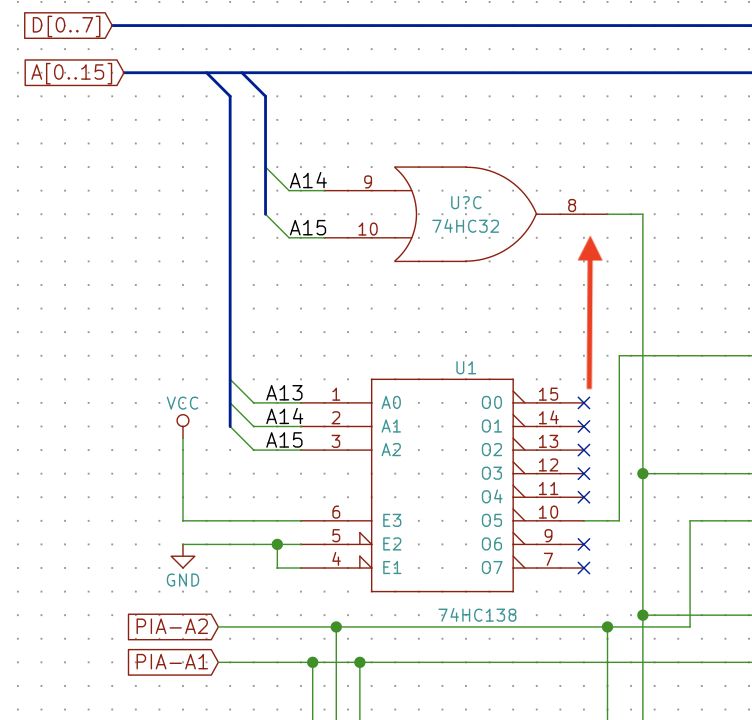

修正した箇所はこちら..

(もともとは固定RAM領域の判断に74HC138のO0端子を使ってました…それだと$0000-1FFFしかデコードできてない….)

固定RAM領域の $2000-3FFFFへ書き込むと 間違って バンクRAMの $6000-7FFFへ書き込まれるという事になってしまっていました….

余っていた74HC32のORゲートを使うことで事なきを得ました。良かった〜♬

コメント