前回、メモリーバンク切り替えのためのバンクレジスタの試作がうまくいきましたので、つぎは128kBメモリーのアドレス線A16/A15をコントロールする方法について検討してみます。

メモリーアドレス線コントロール案

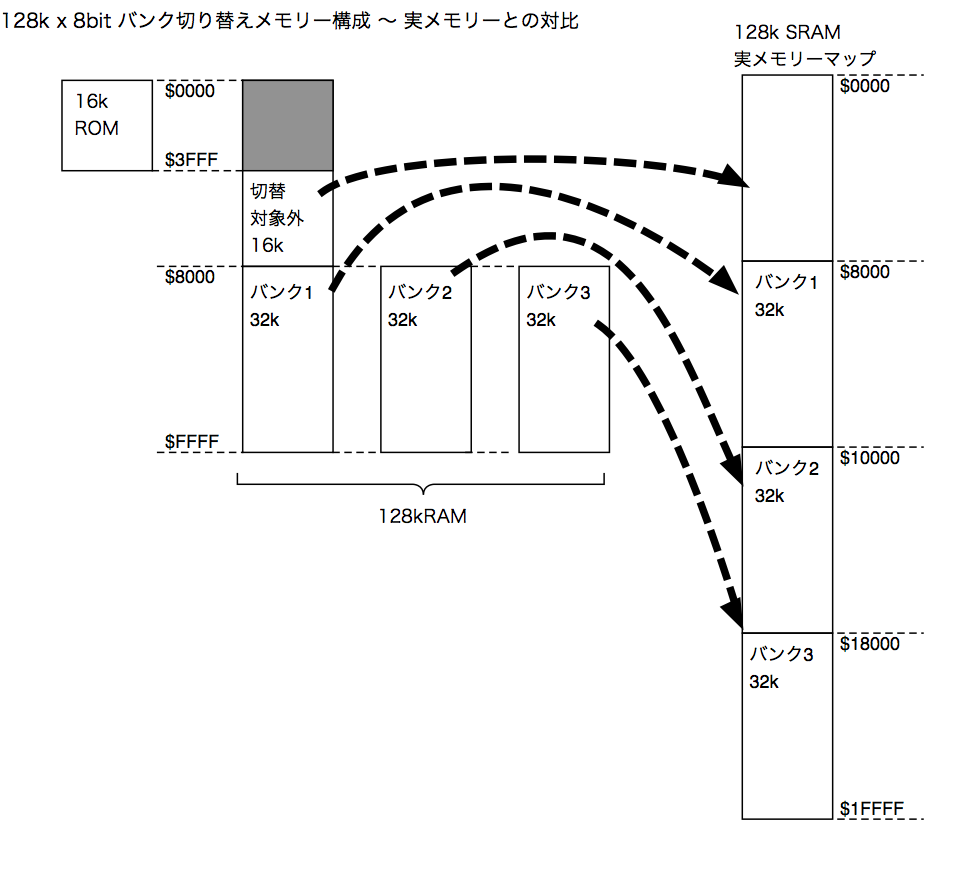

128kB SRAMのうち8000h以上のアドレスについて3分割してバンクメモリーとして使いたいと考えています。

Z80ではアドレスバスとしてはA0〜A15の16本(16bit分)しかコントロールできませんので、前回試作したバンクレジスタの2bitと合わせて上手くコントロールしたいと思います。

想定している真理値表は以下のとおりで、考慮した点は以下になります。

- アドレスバス A15が “L” (つまり0000h〜7FFFh)へアクセスする場合は メモリーのA16/A15共に”L”にする。

- バンクレジスタに何が出力されていても無視です。

- このメモリー領域はROMとRAMで半分づつつかいますが、そのコントロールはCSをコントロールする別の回路にします。

- バンクレジスタへ誤って 0x00を出力された場合でも、デフォルトのバンク1を選択するようにします。

| Z80 A15 | バンクレジスタ DA1 | バンクレジスタ DA0 | 128kメモリー A16 | 128kメモリー A15 | 備考 |

|---|---|---|---|---|---|

| L | x | x | L | L | 0000h〜7FFFhまで |

| H | L | L | L | H | バンクレジスタに0(ゼロ)がセットされた場合 |

| H | L | H | L | L | バンク1 |

| H | H | L | H | L | バンク2 |

| H | H | H | H | H | バンク3 |

これによって以下のように128kB SRAMの全体を有効活用できるようになると考えています。

ロジック回路による実現方法

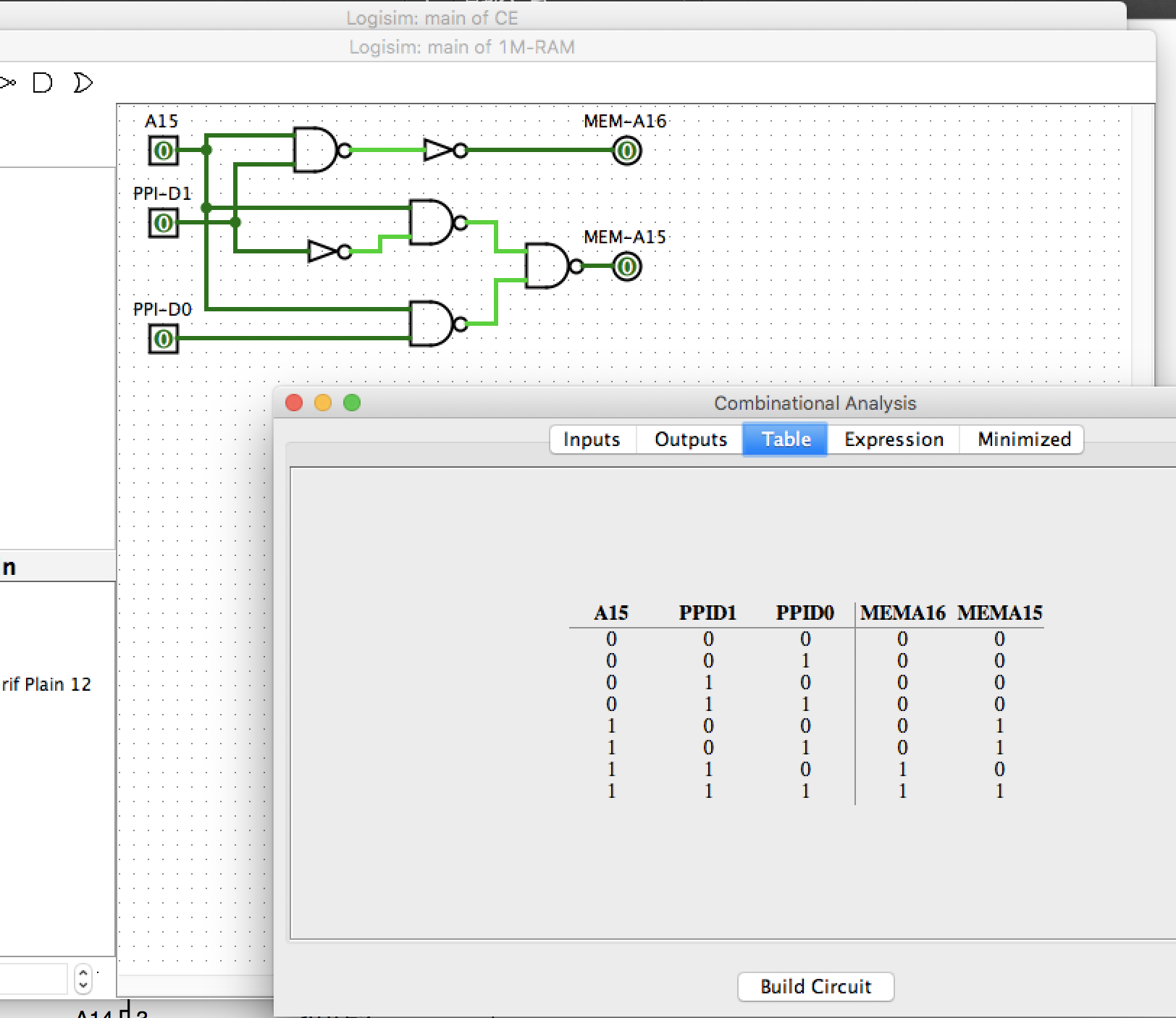

上記の真理値表を使って実際のロジック回路を検討してみます。

Mac上のLogisimを使ってパソコン上で検討しました。

Logisimは真理値表から回路図生成もできまして、オプションで「2入力ゲートを使う」とか「NAND優先」というオプションもあります。

上図はそれで生成してもらった回路です。^^)>

74HC00 x1個と74HC04 x1個の2つのゲートICでコントロールできそうです!

次は実際の基板を作るための回路図を検討します。

コメント

[…] その後は前回の回路図同様 IO書き込み信号(IOWR)と NORゲート(74HC02)を通してラッチ(74HC573)のラッチイネーブル(LE)端子へつなぎます。 […]

[…] メモリーマップは以前の記事でも紹介したとおり、以下のようになっています。 […]